Experts at the Table: Semiconductor Engineering sat down to discuss economic conditions and how that affects chip design with Anirudh Devgan, president and CEO of Cadence; Joseph Sawicki, executive vice president of Siemens EDA; Niels Faché, vice president and general manager at Keysight; Simon Segars, advisor at Arm; and Aki Fujimura, chairman and CEO of D2S. This discussion was held in front of a live audience at the recent Electronic System Design Alliance event. What follows are excerpts of that discussion. To view part one, click here.

SE: We used to think that EDA was recession-proof because design always continues during a downturn? Is that still true?

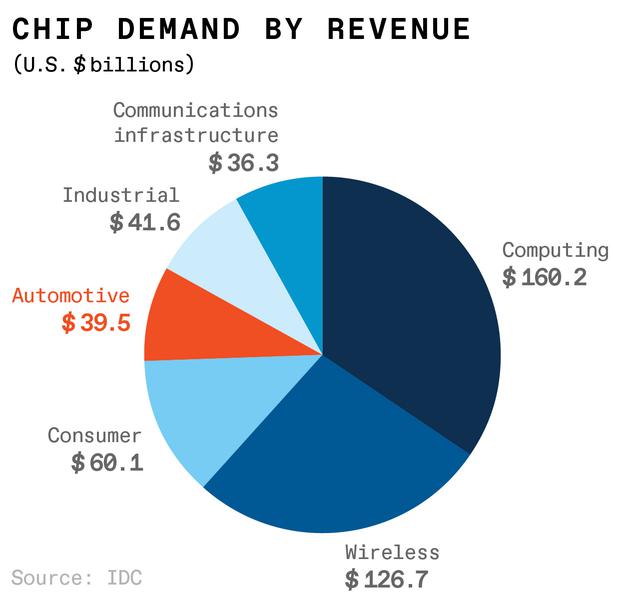

Devgan: It’s true more than ever. In the next five years or so the semiconductor market is expected to double to $1 trillion. That’s good for EDA and for IP. In addition, system companies are designing more silicon, and that’s not going to stop. That’s a good trend for our business. And finally, we’re investing heavily in system-level design and analysis because of the coupling of system level and chip level, and that’s a growing TAM. So there might be some correction, but that would be more on the supply side than on the design side. It’s very difficult to predict that, of course. But if you look at these mega trends, they’re very positive.

Faché: I agree. There are new applications and more industry verticals. That’s all good news. The near term is challenging, with the difference between demand and supply. I was on a recent trip to Europe and talked with some of our semiconductor customers about it. Sometimes they have demand for their products that’s 30% higher than what they can offer. Fabs are fully booked for the next few years, but they are adding capacity. I saw some of that construction. We expect to see equilibrium between supply and demand in the next 18 to 24 months. Beyond that, there is a secular growth trend in our business. There are more applications, more design starts, and new startups. This is a very vibrant market. There are a lot of investments in new projects and new startups. They all need to tool up, and they are all looking for IP that’s in context to the core of their business. And they need consulting services. So we’re in a really good place.

Sawicki: Everyone remembers 10 years ago when everyone said Moore’s Law is dead, or when they said there was never going to be a 90nm node. Design starts were going to collapse to nothing, and only four companies were going to make chips. None of that happened. If anything, design starts are radically increasing. It’s a great time to be in this business. But it’s also challenging, because these are demanding customers.

SE: Moore’s Law isn’t going to end anytime soon, but it is slowing down. We’re seeing a lot more heterogeneous designs in packages. What’s the impact of that?

Devgan: In 1997, I was telling people that system-in-a-package was going to take over system-on-a-chip. It took 25 years for that to happen. System-in-a-package has a lot of advantages. You can have silicon re-use, not just IP re-use. Moore’s Law still can continue for several more generations, which is another 5 to 10 years. So if scaling can continue for 10 years, and you can add 3D-IC on top of that, it can continue to be exponential for another 5 to 10 years. If you look at scaling for the last 5 years, it has been driven by having more things on the chip, not the classical Dennard scaling. 3D-IC is a natural extension of that, and I’m sure the base process can last for at least four or five more generations.

Fujimura: We do GPU acceleration for the semiconductor manufacturing industry, and we build our own GPU platforms because reliability concerns are so great. So we track what’s going on with GPUs quite a bit. NVIDIA just announced its new H100 Processor, which has 17,000 single-precision cores. These are SIMD machines, so you can’t really compare them to CPUs. But compared to two years ago when NVIDIA announced the previous generation, the A100, that had about 7,000, single-precision cores. In two years, it went from 7,000 cores to 17,000 cores. Moore’s Law is different now than in the past. It’s scaling. You’re not getting faster clock speeds, but you are able to compute a lot more on one chip than you were two years ago, and I’m sure that this is going to continue. Intel just announced its semiconductor roadmap, and they’re going to numbers and then to angstroms. But their roadmap goes out way more than 10 years into the future. So this is going to continue. Of course, it’s for very specialized things. When you’re doing IoT devices, you don’t need that. But principally because of deep learning, there’s enormous demand for high-performance computing. That trend is going to continue, and the investment dollars will continue to be available. On the manufacturing side, masks will continue to scale. Lithography to print things on a wafer will continue. But it will be really expensive. So the only question is whether there is an economic justification to continue, because the insatiable demand for computing that deep learning started will continue. This is brute-force computing, and it’s going to be more than just deep learning. You don’t have to be clever. You just go for it.

Segars: If you look at some of the complex IoT devices that people are building right now, these are superscalar processors with very deep pipelines, and they’re quite amazing. In this industry, people are going to find ways of delivering more and more performance in every generation, and there are lots of tools to play with. 3D-IC for these very complex, multi-die packages, adds another dimension or two to the performance. What’s interesting about it, though, is it’s not just more of the same. It isn’t about cranking out more transistors on a chip or making them smaller. It’s about solving different problems. Right now with most chips, the wafer comes out, they get sliced up, the die goes somewhere, somebody else packages them. It’s pretty straightforward, and it’s a very well optimized process. But you’ve got the specter of taking die from different factories, putting them together using some interface that you’re going to work out between them, and standards about how to deal with the substrate. And then you’ve got to drive the cost down, because the people who are doing it today are building very expensive designs that only a few people with very large resources can handle. But this a technology that can apply in lots of places, and the challenge is how to drive that cost out. So that can become something that every designer does, just like writing Verilog today, or firing up a simulator or doing place-and-route. That’s got to become totally mainstream. And then you really will ignite performance, from the smallest microcontroller all the way up to the biggest SoC or chip.

Faché: Cost is a big factor of that I am assuming will get addressed. But there is a good runway for advanced packaging and 3D-IC. Maybe it started with memory on top of CPUs to shorten distances or reduce data transfer delays, but there are a lot more applications outside of the digital domain. When you think about stacking RF and analog circuitry, sensors, and digital content all together, there are lots of applications. So there’s a good future for advanced packaging and 3D-ICs. Of course, it’s putting a lot of emphasis on the tools to support that, as well, and these are very complex designs. When you think about the silicon IP, the interconnects, the packaging, and modeling all the effects, including thermal, parasitic effects, interconnects, we will have to make the tools available.

Sawicki: Dennard scaling is dead. Moore’s Law is fine. But there’s a there’s an interesting metaphor here. So the whole aspect of Dennard scaling dying put a premium for a long period of time on design technology co-optimization — finding ways of optimizing how you’re going to do transistor stacking, how many tracks, how are you going to put these devices together so that you can take this tool or this process that does not inherently give you better performance, and still deliver better performance. As you go to 3D, you need to have design system co-optimization, and we need to start generating tools that allow people to take a look at this in the planning phase. How are you going to be doing your partitioning? What are the performance implications about having the radio in one process versus how much memory you want to put on there, and graft those things together? Are you going to do a silicon substrate or an organic substrate, because that’s going to have a big impact on cost. That’s a set of tools that are newly starting to emerge in this market. It’s about being able to support those architectural-level decisions — again, because it all goes back to what’s the system-level performance — that can be delivered in the application space that a company cares about.

Devgan: 3D-IC is going to be pervasive, and it’s a great opportunity. We have new problems to solve, including thermal effects and electromagnetic effects. It’s going to be multi-technology chips, and the interface IP between chiplets. This is what we want — bigger problems get paid for it.

Related

CEO Outlook: Chip Industry 2022 (Part 1 of above discussion)

Designing for context, and geopolitical impacts on a global supply chain.

Chip Industry Heads Toward $1T

Continued expansion in new and existing markets points to massive and sustained growth.

Slowdown, But No Correction

Materials supply chain still bumpy and consumer buying has peaked for now, but growth continues.

Big Changes In Materials And Processes For IC Manufacturing

Brewer Science’s CTO drills down into everything from purity and bonding to scaling and variation.