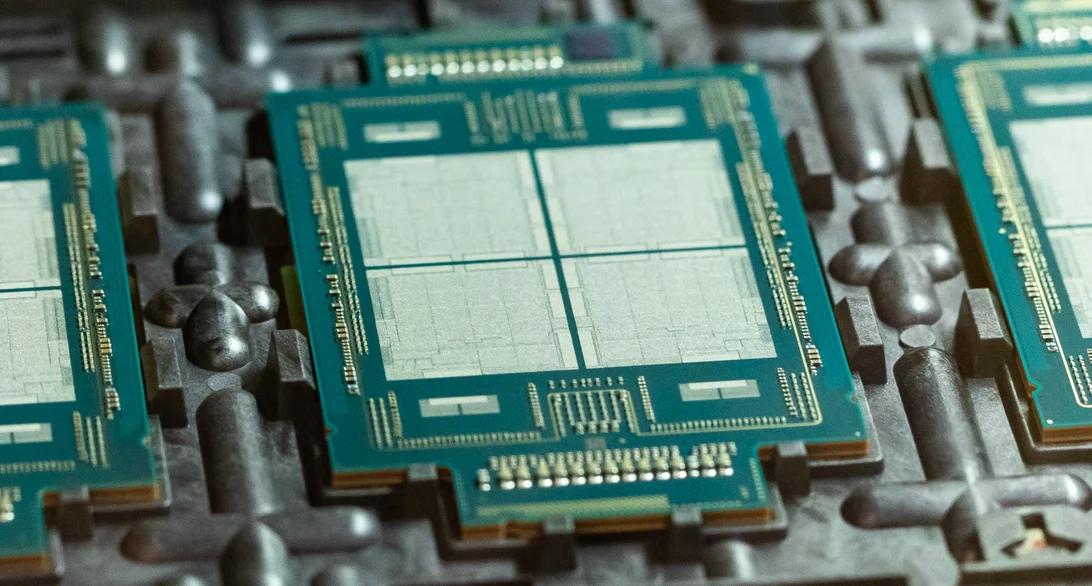

Um chip de teste do lago Intel Meteor de Fab 42.(Créditos da imagem: CNET)

CNET has managed to capture the first die shots of several next-generation Intel Meteor Lake CPUs, Sapphire Rapids Xeons & Ponte Vecchio GPUs that are being tested & produced inside the chipmaker's Fab 42, situated in Arizona, US.

Glorious Die Shots of Intel's Next-Gen Meteor Lake CPUs, Sapphire Rapids Xeons & Ponte Vecchio GPUs Captured at Fab 42 in Arizona

Os tiros foram capturados pelo repórter sênior da CNET, Stephen Shankland, que visitou o Fab 42 da Intel, localizado no Arizona, EUA.Toda a magia acontece aqui, pois a Fabration Factory está produzindo chips de próxima geração para consumidores, data centers e segmentos de computação de alto desempenho.O FAB 42 lidará com os chips de próxima geração da Intel produzidos nos nós do processo de 10 nm (Intel 7) e 7nm (Intel 4).Alguns dos principais produtos que utilizarão esses nós de próxima geração incluem os processadores de clientes do Meteor Lake, os processadores Sapphire Rapids Xeon e Ponte Vecchio GPUs para HPC.

CPUs da AMD Ryzen 7000 podem ter uma vantagem sobre os recursos de memória do Raptor Lake DDR5 da Intel como velocidades nativas de 5200 Mbps listadas para a 13ª geração

Intel 4 Powered Meteor Lake CPUs For Client Computing

O primeiro produto a falar é o Meteor Lake.Indo para PCs para desktop do cliente em 2023, as CPUs Meteor Lake será o primeiro design de multi-chipleto verdadeiro da Intel.A CNET conseguiu tirar fotos dos primeiros chips de teste do lago meteor.O veículo de teste do lago Meteor, na foto acima, é usado para garantir que o design da embalagem FORVEROS funcione corretamente e como esperado.O Meteor Lake CPUS utilizará a tecnologia de embalagem Forveos da Intel para interconectar os vários IPs do núcleo integrado no chip.

Intel Meteor Lake Test Chips Prepare Chipzilla para a produção final de CPUs Core de próxima geração.(Créditos da imagem: CNET)

O dado tem quatro chipets que estão conectados no mesmo substrato.Com base no que a Intel mostrou em suas renderizações, o dado superior deve ser o ladrilho de computação, o azulejo do meio deve ser o ladrilho SOC-LP e o dado mais baixo deve ser o ladrilho da GPU.No entanto, com base nos tamanhos dos matrizes, isso não vai bem.O dado médio pode ser o ladrilho de computação principal que abriga os núcleos e o dado menor abaixo, pode ser o telha do SOC-LP que inclui o IO.O dado superior deve ser a GPU, enquanto o morto menor ao lado dela pode ser um cache separado ou outro azulejo de IO.Isso é apenas uma especulação pura por enquanto, pois são chips de teste e o design final pode acabar sendo diferente.

Também damos uma primeira olhada no Wafer de Teste do Meteor Lake, que mede 300 mm na diagonal.A bolacha compreende chips de teste que são falsos, mais uma vez para garantir que as interconexões no chip funcionem como pretendido.A Intel já alcançou o poder do seu meteoro Lake Compute CPU Tile, para que possamos esperar que os chips finais sejam produzidos no dia 2 de 2022 para lançamento em 2023.

Intel adds Arc GPU, Rocky Linux, & multi-GPU functionality support to oneVPL 2022.1

Here's Everything We Know About The 14th Gen Meteor Lake 7nm CPUs

Já temos alguns detalhes da Intel, como o fato de que a linha de comprimidos de desktop e mobilidade de Intel deve se basear em uma nova linha de arquitetura de núcleo de enseada.Há rumores de que isso seja conhecido como 'Redwood Cove' e será baseado em um nó de processo de 7nm EUV.Afirma -se que o Redwood Cove foi projetado desde o solo para ser um nó agnóstico, o que significa que ele pode ser fabricado em diferentes FABs.Há referências mencionadas que apontam para o TSMC ser um backup ou mesmo um fornecedor parcial para os chips baseados em Redwood Cove.Isso pode nos dizer por que a Intel está declarando vários processos de fabricação para a família CPU.

As CPUs do Meteor Lake pode ser a primeira geração da CPU da Intel a dizer adeus à arquitetura de interconexão do barramento do anel.Também há rumores de que o Meteor Lake poderia ser um design totalmente empilhado em 3D e poderia utilizar uma matriz de E/S proveniente de um Fab externo (TSMC avistado novamente).É destacado que a Intel estará utilizando oficialmente sua tecnologia de embalagem Foveros na CPU para interconectar as várias matrizes no chip (XPU).Isso também está alinhado com a Intel referindo -se a cada ladrilho em chips de 14ª geração individualmente (ladrilhos de computação = núcleos da CPU).

The Meteor Lake Desktop CPU family is expected to retain support on the LGA 1700 socket which is the same socket used by Alder Lake & Raptor Lake processors.Podemos esperar a memória DDR5 e o PCIE Gen 5.0 suporte. The platform will support both DDR5 & DDR4 memory with the mainstream and budget tier options going for DDR4 memory DIMMs while the premium & high-end offerings going for DDR5 DIMMs.O site também lista as CPUs Meteor Lake P e Meteor Lake M, que serão destinadas a plataformas de mobilidade.

Intel Mainstream Desktop CPU Generations Comparação:

| Intel CPU Family | Processor Process | Processors Cores/Threads (Max) | TDPs | Platform Chipset | Platform | Memory Support | PCIe Support | Launch |

|---|---|---|---|---|---|---|---|---|

| Sandy Bridge (2nd Gen) | 32nm | 4/8 | 35-95W | 6-Series | LGA 1155 | DDR3 | PCIe Gen 2.0 | 2011 |

| Ivy Bridge (3rd Gen) | 22nm | 4/8 | 35-77W | 7-Series | LGA 1155 | DDR3 | PCIe Gen 3.0 | 2012 |

| Haswell (4th Gen) | 22nm | 4/8 | 35-84W | 8-Series | LGA 1150 | DDR3 | PCIe Gen 3.0 | 2013-2014 |

| Broadwell (5th Gen) | 14nm | 4/8 | 65-65W | 9-Series | LGA 1150 | DDR3 | PCIe Gen 3.0 | 2015 |

| Skylake (6th Gen) | 14nm | 4/8 | 35-91W | 100-Series | LGA 1151 | DDR4 | PCIe Gen 3.0 | 2015 |

| Kaby Lake (7th Gen) | 14nm | 4/8 | 35-91W | 200-Series | LGA 1151 | DDR4 | PCIe Gen 3.0 | 2017 |

| Coffee Lake (8th Gen) | 14nm | 6/12 | 35-95W | 300-Series | LGA 1151 | DDR4 | PCIe Gen 3.0 | 2017 |

| Coffee Lake (9th Gen) | 14nm | 8/16 | 35-95W | 300-Series | LGA 1151 | DDR4 | PCIe Gen 3.0 | 2018 |

| Comet Lake (10th Gen) | 14nm | 10/20 | 35-125W | 400-Series | LGA 1200 | DDR4 | PCIe Gen 3.0 | 2020 |

| Rocket Lake (11th Gen) | 14nm | 8/16 | 35-125W | 500-Series | LGA 1200 | DDR4 | PCIe Gen 4.0 | 2021 |

| Alder Lake (12th Gen) | Intel 7 | 16/24 | 35-125W | 600 Series | LGA 1700 | DDR5 / DDR4 | PCIe Gen 5.0 | 2021 |

| Raptor Lake (13th Gen) | Intel 7 | 24/32 | 35-125W | 700-Series | LGA 1700 | DDR5 / DDR4 | PCIe Gen 5.0 | 2022 |

| Meteor Lake (14th Gen) | Intel 4 | TBA | 35-125W | 800 Series? | TBA | DDR5 | PCIe Gen 5.0? | 2023 |

| Arrow Lake (15th Gen) | Intel 20A | 40/48 | TBA | 900-Series? | TBA | DDR5 | PCIe Gen 5.0? | 2024 |

| Lunar Lake (16th Gen) | Intel 18A | TBA | TBA | 1000-Series? | TBA | DDR5 | PCIe Gen 5.0? | 2025 |

| Nova Lake (17th Gen) | Intel 18A | TBA | TBA | 2000-Series? | TBA | DDR5? | PCIe Gen 6.0? | 2026 |

Intel 7 Powered Sapphire Rapids CPUs For Xeon Data Center & Servers

Também obtemos uma visão mais detalhada do substrato da Intel Sapphire Rapids-Sp Xeon CPU, Chiplets e design completo de pacotes (variantes padrão e HBM).A variante padrão apresenta quatro ladrilhos que incorporarão os chiplets de computação.Existem também quatro pin-outs para os pacotes HBM.O chip se comunicará com todos os 8 chipets (quatro computadores / quatro HBM) através de interconexões do EMIB, que são as barras retangulares menores na borda de cada matriz.

A substrate of the Intel Sapphire Rapids-SP Xeon CPU with HBM2e memory.(Créditos da imagem: CNET)O produto final pode ser visto abaixo e mostra os quatro telhas de computação Xeon no meio com quatro pacotes menores HBM2 nas laterais.A Intel confirmou recentemente que a Sapphire Rapids-Sp Xeon CPUS apresentará até 64 GB de memória hbm2e a bordo das CPUs.Este é o design da CPU de pleno direito mostrado aqui e mostra que está pronto para implantação em data centers de próxima geração até 2022.

The final 4th Gen Sapphire Rapids-SP Xeon CPU with its multi-chiplet design housing Compute & HBM2e tiles.(Créditos da imagem: CNET)Here's Everything We Know About The 4th Gen Intel Sapphire Rapids-SP Xeon Family

De acordo com a Intel, o Sapphire Rapids-Sp virá em duas variantes de pacotes, um padrão e uma configuração HBM.A variante padrão apresentará um design de chiplet composto por quatro matrizes XCC que apresentarão um tamanho de matriz de cerca de 400mm2.Este é o tamanho do dado para um dado singular xcc e haverá quatro no total no topo do chip Xeon Sapphire Rapids-Sp Xeon.Cada dado será interconectado via EMIB, que tem um tamanho de pitch de 55U e um tom central de 100U.

O chip Xeon Sapphire Rapids-Sp.Mudando para a variante HBM, estamos obtendo um número aumentado de interconexões que estão em 14 e são necessárias para interconectar a memória HBM2E aos núcleos.

Os quatro pacotes de memória HBM2E apresentarão pilhas de 8 hi, então a Intel está custando pelo menos 16 GB de memória HBM2E por pilha para um total de 64 GB no pacote Sapphire Rapids-Sp.Falando sobre o pacote, a variante HBM medirá em uma loucura 5700mm2 ou 28% maior que a variante padrão.Comparado aos números de Epyc Gênova recentemente vazados, o pacote HBM2E para Sapphire Rapids-SP acabará 5% maior, enquanto o pacote padrão será 22% menor.

A Intel também afirma que o link do EMIB fornece o dobro da melhoria da densidade de largura de banda e 4 vezes melhor eficiência de energia em comparação com os projetos de pacotes padrão.É interessante. You can read the full details regarding the standard 56 core & 112 thread Sapphire Rapids-SP Xeon CPUs here.

Famílias Intel Xeon SP (preliminares):

| Family Branding | Skylake-SP | Cascade Lake-SP/AP | Cooper Lake-SP | Ice Lake-SP | Sapphire Rapids | Emerald Rapids | Granite Rapids | Diamond Rapids |

|---|---|---|---|---|---|---|---|---|

| Process Node | 14nm+ | 14nm++ | 14nm++ | 10nm+ | Intel 7 | Intel 7 | Intel 3 | Intel 3? |

| Platform Name | Intel Purley | Intel Purley | Intel Cedar Island | Intel Whitley | Intel Eagle Stream | Intel Eagle Stream | Intel Mountain Stream Intel Birch Stream | Intel Mountain Stream Intel Birch Stream |

| Core Architecture | Skylake | Cascade Lake | Cascade Lake | Sunny Cove | Golden Cove | Raptor Cove | Redwood Cove? | Lion Cove? |

| IPC Improvement (Vs Prev Gen) | 10% | 0% | 0% | 20% | 19% | 8%? | 35%? | 39%? |

| MCP (Multi-Chip Package) SKUs | No | Yes | No | No | Yes | Yes | TBD (Possibly Yes) | TBD (Possibly Yes) |

| Socket | LGA 3647 | LGA 3647 | LGA 4189 | LGA 4189 | LGA 4677 | LGA 4677 | TBD | TBD |

| Max Core Count | Up To 28 | Up To 28 | Up To 28 | Up To 40 | Up To 56 | Up To 64? | Up To 120? | Up To 144? |

| Max Thread Count | Up To 56 | Up To 56 | Up To 56 | Up To 80 | Up To 112 | Up To 128? | Up To 240? | Up To 288? |

| Max L3 Cache | 38.5 MB L3 | 38.5 MB L3 | 38.5 MB L3 | 60 MB L3 | 105 MB L3 | 120 MB L3? | 240 MB L3? | 288 MB L3? |

| Vector Engines | AVX-512/FMA2 | AVX-512/FMA2 | AVX-512/FMA2 | AVX-512/FMA2 | AVX-512/FMA2 | AVX-512/FMA2 | AVX-1024/FMA3? | AVX-1024/FMA3? |

| Memory Support | DDR4-2666 6-Channel | DDR4-2933 6-Channel | Up To 6-Channel DDR4-3200 | Up To 8-Channel DDR4-3200 | Up To 8-Channel DDR5-4800 | Up To 8-Channel DDR5-5600? | Up To 12-Channel DDR5-6400? | Up To 12-Channel DDR6-7200? |

| PCIe Gen Support | PCIe 3.0 (48 Lanes) | PCIe 3.0 (48 Lanes) | PCIe 3.0 (48 Lanes) | PCIe 4.0 (64 Lanes) | PCIe 5.0 (80 lanes) | PCIe 5.0 (80 Lanes) | PCIe 6.0 (128 Lanes)? | PCIe 6.0 (128 Lanes)? |

| TDP Range (PL1) | 140W-205W | 165W-205W | 150W-250W | 105-270W | Up To 350W | Up To 375W? | Up To 400W? | Up To 425W? |

| 3D Xpoint Optane DIMM | N/A | Apache Pass | Barlow Pass | Barlow Pass | Crow Pass | Crow Pass? | Donahue Pass? | Donahue Pass? |

| Competition | AMD EPYC Naples 14nm | AMD EPYC Rome 7nm | AMD EPYC Rome 7nm | AMD EPYC Milan 7nm+ | AMD EPYC Genoa ~5nm | AMD Next-Gen EPYC (Post Genoa) | AMD Next-Gen EPYC (Post Genoa) | AMD Next-Gen EPYC (Post Genoa) |

| Launch | 2017 | 2018 | 2020 | 2021 | 2022 | 2023? | 2024? | 2025? |

Intel 7 Powered Ponte Vecchio GPUs For HPC

Por fim, temos uma excelente visão da Intel Ponte Vecchio GPU, a solução HPC da próxima geração.Ponte Vecchio foi projetado e criado sob a liderança de Raja Koduri, que está nos fornecendo ótimos boatos sobre a filosofia de design e o poder de computação insano que este chip pacote.

Intel's Ponte Vecchio is a gold mine of chiplets, housing over 47 different tiles on the same package.(Créditos da imagem: CNET)Here's Everything We Know About The Intel 7 Powered Ponte Vecchio GPUs

Mudando-se para Ponte Vecchio, a Intel descreveu alguns recursos importantes de sua GPU de data center principal, como 128 núcleos XE, 128 unidades RT, memória HBM2E e um total de 8 GPUs XE-HPC que serão conectados juntos.O chip apresentará até 408 Mb de cache L2 em duas pilhas separadas que se conectarão através da interconexão do EMIB.O chip apresentará várias matrizes com base no próprio processo 'Intel 7' da Intel e nos nós do processo N7 / N5 da TSMC.

A Intel também anteriormente detalhou o pacote e o tamanho da matriz de sua principal GPU Ponte Vecchio com base na arquitetura XE-HPC.O chip consistirá em 2 telhas com 16 matrizes ativas por pilha.O tamanho máximo de matriz superior ativo será 41mm2, enquanto o tamanho da matriz base, que também é chamado de 'ladrilho de computação', fica a 650mm2.Temos todos os chiplets e nós de processo que as GPUs de Ponte Vecchio utilizarão, listadas abaixo:

A seguir, é como a Intel chega a 47 azulejos no chip Ponte Vecchio:

A GPU Ponte Vecchio faz uso de 8 pilhas de 8 hi HBM e contém um total de 11 interconexões emib.Todo o pacote Intel Ponte Vecchio mediria 4843.75mm2.Também é mencionado que o pitch bump for meteor lake cpus usando embalagem 3D de alta densidade será 36U.

The Ponte Vecchio GPU will be competing against NVIDIA and AMD HPC GPUs in 2022.(Créditos da imagem: CNET)A GPU de Ponte Vecchio não é 1 chip, mas uma combinação de várias fichas.É uma potência de chiplet, empacotando mais chipets em qualquer GPU/CPU por aí, 47 para ser preciso.E estes não são baseados em apenas um nó de processo, mas vários nós de processo, pois tínhamos detalhado apenas alguns dias atrás.

Aceleradores de GPU de data center de próxima geração

| GPU Name | AMD Instinct MI250X | NVIDIA Hopper GH100 | Intel Ponte Vecchio |

|---|---|---|---|

| Packaging Design | MCM (Infinity Fabric) | Monolithic | MCM (EMIB + Foveros) |

| GPU Architecture | Aldebaran (CDNA 2) | Hopper GH100 | Xe-HPC |

| GPU Process Node | 6nm | 4N | 7nm (Intel 4) |

| GPU Cores | 14,080 | 16,896 | 16,384 ALUs (128 Xe Cores) |

| GPU Clock Speed | 1700 MHz | ~1780 MHz | TBA |

| L2 / L3 Cache | 2 x 8 MB | 50 MB | 2 x 204 MB |

| FP16 Compute | 383 TOPs | 2000 TFLOPs | TBA |

| FP32 Compute | 95.7 TFLOPs | 1000 TFLOPs | ~45 TFLOPs (A0 Silicon) |

| FP64 Compute | 47.9 TFLOPs | 60 TFLOPs | TBA |

| Memory Capacity | 128 GB HBM2E | 80 GB HBM3 | 128 GB HBM2e |

| Memory Clock | 3.2 Gbps | 3.2 Gbps | TBA |

| Memory Bus | 8192-bit | 5120-bit | 8192-bit |

| Memory Bandwidth | 3.2 TB/s | 3.0 TB/s | ~3 TB/s |

| Form Factor | OAM | OAM | OAM |

| Cooling | Passive Cooling Liquid Cooling | Passive Cooling Liquid Cooling | Passive Cooling Liquid Cooling |

| TDP | 560W | 700W | TBD |

| Launch | Q4 2021 | 2H 2022 | 2022? |

O Fab 42 da Intel deve logo se fundir com o próximo Fab 52 e Fab 62 nos próximos anos, que estarão produzindo o que vem a seguir.O CEO da Intel, Pat Gelsinger, já quebrou o chão nos Fabs em setembro e é aqui que você verá a produção dos produtos da próxima geração Sub-Intel 7.

Roteiro do processo da Intel

| Process Name | Intel 10nm SuperFin | Intel 7 | Intel 4 | Intel 3 | Intel 20A | Intel 18A |

|---|---|---|---|---|---|---|

| Production | In High-Volume (Now) | In Volume (Now) | 2H 2022 | 2H 2023 | 2H 2024 | 2H 2025 |

| Perf/Watt (over 10nm ESF) | N/A | 10-15% | 20% | 18% | >20%? | TBA |

| EUV | N/A | N/A | Yes | Yes | Yes | High-NA EUV |

| Transistor Architecture | FinFET | Optimized FinFET | Optimized FinFET | Optimized FinFET | RibbonFET | Optimized RibbonFET |

| Products | Tiger Lake | Alder Lake Raptor Lake Sapphire Rapids Emerald Rapids Xe-HPG? | Meteor Lake Xe-HPC / Xe-HP? | Granite Rapids Sierra Forest TBA | Arrow Lake Diamond Rapids? TBA | Lunar Lake Nova Lake TBA TBA |

Fonte de notícias: CNET