Intel se précipite pour regagner ses bases en tant que leader incontesté dans la technologie de fabrication des puces d'ici 2025.

La société basée à Santa Clara, en Californie, a récemment publié l'une de ses feuilles de route les plus ambitieuses depuis des années, pleine de nouvelles technologies de processus et d'emballage qui, selon Intel, combleront l'écart de performance avec des rivaux d'ici 2024 et lui donnent un leadership technologique des processus d'ici 2025.L'objectif est de déployer une nouvelle génération de processeurs - et un nouveau nœud de processus pour le produire en masse - chaque année jusqu'en 2025.

Chaque génération de processeurs sera basée sur des transistors plus avancés que le dernier.Intel a déclaré qu'il apportait des fonctionnalités dans le pli à chaque étape de la feuille de route, y compris une nouvelle architecture de transistor appelé Rubbonfet d'ici 2024 et un nouveau système d'interconnexion appelé Powervia la même année.Il étend également l'utilisation de la lithographie EUV à chaque nœud et prévoit de battre ses concurrents hors de la porte avec l'EUV "High-NA".

La société a révélé la nouvelle feuille de route du processus et de l'emballage lors de son événement «Intel accéléré» le mois dernier.

Intel a glissé du point de direction de l'industrie des semi-conducteurs ces dernières années.Derrière les malheurs d'Intel se trouvent des aséries de fabrication de faux pas qui l'ont forcé à retarder ses processeurs les plus avancés pour les centres de données et les ordinateurs personnels.En février, Intel a embauché son ancien directeur de la technologie Pat Gelsinger en tant que PDG pour revigorer son processus de développement des puces et reprendre le terrain.

Parce qu'il a entraîné le développement de son nœud de 10 nm pendant des années, Intel est tombé derrière SMC dans sa capacité à produire en masse les puces les plus avancées.TSMC l'a battu sur le marché plus large avec son nœud de 7 nm, puis a sauté vers une autre génération avec son processus de 5 nm, qui a d'abord été adopté par Apple.TSMC est la plus grande fonderie de puces au monde avec plus de 500 clients, dont de nombreux principaux rivaux d'Intel.

Des retards prolongés ont ouvert la porte à une horde croissante de rivaux, notamment AMD et ARM à la domination de Dent Intel dans les ordinateurs personnels et les centres de données.L'effondrement d'Intel a soulevé des questions sur la question de savoir si elle élargirait son utilisation des fonderies - ou démantèle ses opérations de fabrication en faveur de l'externalisation davantage de sa production - pour l'empêcher de prendre plus de retard et de perdre plus de commandes d'Apple et AWS.

Mais Intel a doublé sur ses activités de fabrication avec l'annonce de son IDM 2.0 Stratégie, qui sera le géant de la Silicon Valley Garder la majeure partie de sa production en interne et investir des dizaines de milliards de dollars dans ses SAB semi-conducteurs.

L'un des piliers du plan de redressement consiste à étendre ses opérations de fabrication, à commencer par 20 milliards de dollars pour construire son u.S.Fabs, donnant à l'entreprise la capacité de répondre à ses propres besoins et de produire en masse sous contrat pour d'autres entreprises et même ses concurrents.Intel a également formé une unité commerciale de fonderie, appelée IFS, et envisageant une montée en puissance de son utilisation de la fonderie, y compris pour certains de ses processeurs les plus avancés à partir de 2023.

Mais au cœur de la stratégie se trouve une reconstruction anagressive des prouesses manufacturières d'Intel."En s'appuyant sur le leadership de l'intestins d'Intel dans l'emballage avancé, nous accélérons la feuille de route OurInnovation pour nous assurer que nous sommes sur une voie claire pour traiter la lecture de performance d'ici 2025", a déclaré Gelsinger."Nous serons implacables dans notre poursuite de la loi de Moore."

Intel ajuste également la nomenclature du nœud basé sur le tânomètre que l'entreprise semi-conducteurs a utilisé des Fordades.L'entreprise renommera ses nœuds de processus pour mieux s'aligner sur les normes d'industrie.

Aujourd'hui, le processeur le plus avancé jusqu'à des dizaines de milliards de transistors servant de minuscules commutateurs électroniques contrôlent le flux de courant.Chaque transistor contient un mont de porte du canal du canal que le courant traverse, pontant les côtés "source" et "drainer" d'un canal.Une porte est utilisée pour contrôler le courant qui traverse le canal et détermine si le transistor est dans un état «ON» ou «OFF».

Pendant des années, la porte a été la dimension la plus importante pour déterminer les performances d'un transistor, et le nombre de Node de processus correspondait aux dimensions de la porte ou des parties de l'anatomie du transistor.Même si Intel a continué à user les nœuds basés sur le nanomètre, les noms ne se réfèrent plus à la largeur du longueur de la porte ou à l'un des autres composants internes du transistor.

Aujourd'hui, la densité du transistor est le themétrique utilisé par les experts pour comparer différents nœuds.Intel a longtemps étendu sa technologie de processus peut égaler ou battre les performances des nœuds numérotés de la même manière de TSMC et d'autres rivaux en termes de densité de transistors qui peuvent tenir sur un carré de silicium.Selon les analystes de l'industrie, le nœud de 10 nm d'Intel est à peu près au même niveau que le processus de 7 nm de TSMC en densité de transistor.

Intel a déclaré que le nouveau format de dénomination des nœuds apportera plus de clarté aux clients, y compris les clients potentiels de son entreprise de fond et les aider à comprendre comment le nouveau processus technologique.Ann Kelleher, SVP de développement de la technologie d'Intel, a déclaré que les nouveaux noms donnent plus de poids aux métriques telles que l'asperformance, l'efficacité énergétique et la zone pendant la transistordentité.

La nouvelle feuille de route traverse les nœuds Fourtechnology Intel prévoit de déployer après son nœud "Superfin" de 10 nm, qui est utilisé dans sa nouvelle génération de processeurs mobiles, code nommé "Tiger Lake", introduit en 2020.

«Intel 7» est ce que l'entreprise Plansto appelle son processus de «superfin amélioré» de 10 nm, qui sera utilisé pour éliminer les processeurs de composition personnels «Alder Lake» dans la seconde moitié de 2021 et des processeurs «Sapphire Rapids» pour les centres de données, qui sont en cours pour être en production au premier trimestre de 2022.Intel a amélioré les transistors FinFet pour apporter une augmentation de 10% à 15% des performances par watt par rapport à son nœud superfin précédent.

Intel a déclaré que les processeurs "Alder Lake" sont en cours de production de masse avec le nœud SuperFin amélioré, qui époise la loi de performance de Moore Outanother du nœud de 10 nm pour justifier l'utilisation du nom "Intel7".

"Intel 4" est la technologie de la technologie anciennement connue sous le nom de processus de 7 nm, qu'Intel a été tristement forcé Todelay à 2023 en raison de défauts dans le processus de production.La société a précédemment déclaré que ses futurs processeurs «Meteor Lake» seraient assemblés à partir de tuiles de calcul sur le nœud de 7 nm.Le nœud profiterait pleinement de l'EUV pour imprimer les plus petits transistors sur les plaquettes de silicium en utilisant des longueurs d'onde ultra-court de lumière - et dans l'extérieur qui réduit le risque d'imperfections qui peuvent ruiner le produit final, améliorant les rendements.

Intel a déclaré que le nœud aurait 20% de performance par-par-botté que son prédécesseur sur la feuille de route, ainsi que les améliorations de la zone.Selon la société, elle serait prête à la seconde de 2022 afin que les puces commencent à expédier en 2023, y compris ses processeurs «Meteorlake» pour le marché des ordinateurs personnels et ses processeurs «Granite Rapids» pour Data-Centerservers.Les puces de test sont actuellement en laboratoire.

«Intel 3» est ce que Intel a précédemment appelé son nœud 7 nm +, son nœud technologique final basé sur les transistors FinFet.Intel a déclaré qu'il commencerait à déployer des puces en fonction du nœud par le secondhalf de 2023, offrant environ 18% de meilleures performances par watt.Le nœud "Intel 3" apporte une technologie de transistor plus avancée dans THEFOLD et une bibliothèque haute performance pour aider à la mise à l'échelle de la zone.Intel expose également l'utilisation par le nœud de l'équipement EUV.

Intel s'appuie sur ses 2.Arsenal d'emballage avancé 5D et 3D pour aider à combler son écart de performance avec des concurrents.Italie a introduit de nouvelles versions de sa technologie Foveros 3D d'empilement de puces définir la production de Formass d'ici 2023.

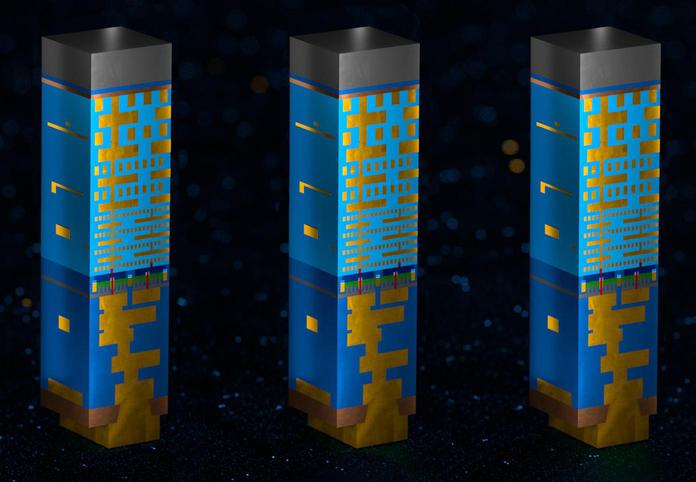

L'arrêt final sur la nouvelle feuille de route est le nœud "Intel 20A", qui, selon le vendeur.Le "A" dans le nœud représente "Angstrom", ou sur le plan du nanomètre.Auparavant connu sous le nom de nœud de 5 nm, Intel a déclaré que 20A profiterait de son avantage de ses technologies RibbonFet et PowerVia pour le mettre à la «parité» avec les futurs nœuds de TSMC et Samsung.

Le rubanfet est la première architecture NewTransistor d'Intel depuis qu'il a introduit le Finfet il y a dix ans.Un finfetis formé en appliquant une bride de silicium en forme de nageoire pour connecter les côtés source et drain du canal dans le transistor.La porte - la région qui détermine si le transistor est allumé ou désactivé - est drapé sur la nageoire, l'entourant sur trois côtés.Cette architecture aide à réduire la fuite de puissance du transistor.Ces minuscules commutateurs peuvent s'allumer et s'éteindre plus rapidement et gaspiller moins de puissance que les transistors planaires.

Le Finfet a été le cheval de bataille des puces avancées au cours de la dernière décennie de la loi de Moore.Le rubanfet et d'autres transistors à tous les promesses promettent de saisir plus de performances dans une zone plus petite sans envoyer de besoins en puissance à travers le toit.Dans les rubanes, la nageoire est inversée sur le côté de sorte que la porte entoure le canal en forme de ruban de tous les côtés, empêchant la puissance supplémentaire de fuir.Intel a déclaré que ces types de transistors offrent des vitesses de commutation plus rapides dans le même entraînement des ailerons Asmultiples dans une empreinte plus petite.

Intel Said Powervia est le premier système de «livraison de puissance arrière».Aujourd'hui, les puces logiques avancées la plus importantes contiennent des milliards de transistors couverts par une canne en couches d'interconnexions de dimensions variables qui fournissent des signaux et fournissent des puissances entre eux.Les interconnexions sont formées en sculptant de minuscules tranchées hors d'une tranche, en les enroguant de cobalt et d'autres métaux, et de les brancher avec des cornes de cuivre.

Le problème qu'Intel essaie de Toaddress avec PowerVia est que les signaux de relais et la puissance sont emmêlés dans la même pile d'interconnexions.Mais avec Powervia Technology, les fils envoyant de l'énergie autour de la puce sont placés derrière les transistors à l'arrière de la tranche.Ainsi, la puissance peut désormais être livrée directement aux transistors plutôt que de parcourir une distance plus longue à travers les planchers et les étages d'interconnexions.

En relocalisant ces fils de l'autre côté de la tranche, la technologie Powervia libère les fils sur le frontside de la tranche pour améliorer le routage du signal.Les résultats sont une meilleure puissance et des fréquences plus élevées.

Le géant des semi-conducteurs est également au début du développement du nœud de processus «18A», qui est ciblé pour la production dans la première moitié de 2025.Intel a déclaré qu'il prévoyait d'améliorer les transistors rubanfet au cœur du nœud de processus, entraînant un autre saut majeur de performance.Intel a déclaré que le nœud 18A est sur le rythme pour être plus avancé que les futurs nœuds de TSMC, le renvoyant pour traiter le leadership technologique.

Intel s'est également associé au fournisseur d'équipement avec le fournisseur de l'équipement de l'émiCducteur sur le développement de nouveaux outils EUV à haute numericalaperture (NA) qui peuvent brûler des transistors plus petits dans des jetons plus rapidement et plus efficacement que la technologie EUV utilisée aujourd'hui.Intel a déclaré qu'Itxpecte d'obtenir le premier outil EUV élevé de production dans l'industrie et d'utiliser ITON ses lignes de production d'ici 2025 ou plus tard.

Malgré le rythme ambitieux de sa feuille de route de la technologie du New Process, Intel joue au rattrapage.TSMC a commencé à fournir des puces basées sur sa technologie de 5 nm, tandis que certains clients sont inférieurs précoces avec des puces basées sur son nœud à 3 nm.Cela signifie que AMD, NVIDIA, Qualcomm, Xilinx et d'autres sociétés de puces peuvent continuer à commander des puces qui sont moradères que celles d'Intel - et elles devraient pouvoir être en mesure de plus de trois ans de plus.

De toute évidence, à mesure que la création de puces devient plus expédiée et technologiquement difficile, la nouvelle feuille de route d'Intel n'est pas garantie.

Mais l'industrie technologique ne fait pas encore comprendre.La société a déclaré qu'elle avait atterri Qualcomm en tant que client de fonderie pour le nœud 20A qui sortira en 2024.Il a également annoncé que le AWAMAZON AWS avait accepté d'adopter la technologie avancée de l'emballage, Intel prévoit des clients aux clients de sa nouvelle entreprise de puce sur commande.