Je ne pouvais pas m'empêcher de remarquer que dans la présentation Cxl, Intel a donné aujourd'hui un indice sur l'avenir de ses ambitions Xe GPU. While it was not explicitly stated anywhere - it seems to have a pretty obvious implication to me; time to coin a term: Coherent Multi-GPU.Cxl est la nouvelle couche d'interconnexion d'Intel qui est conçue pour résoudre de nombreux problèmes avec le protocole PCIE et l'une des principales raisons pour lesquelles le multi-GPU n'a jamais décollé est dû au manque de - vous l'avez deviné - la cohérence.Je pense qu'il est très probable que nous verrons Xe GPU fonctionner en "mode Cxl" à l'avenir.

Intel Cxl in a nutshell: Heterogenous compute protocol for scaling processors over PCIe Gen 5 and beyond

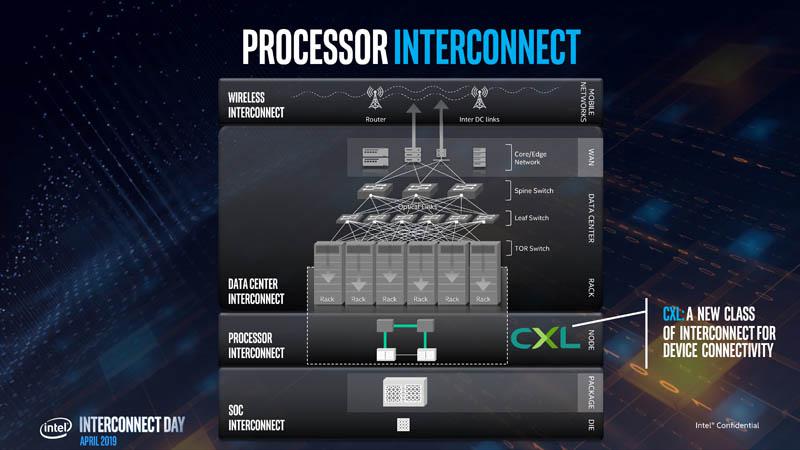

Intel a discuté de sa toute nouvelle interconnexion de processeur à processeur, appelé le Calcule Express Link (Cxl), en détail lors de l'événement «Interconnect Day 2019» hier. Whereas we have talked in depth about data centre interconnects before, this particular one works to connect devices across the physical PCIe port. The reason why I mention physical and not just PCIe is because while Intel Cxl is designed to work over the physical PCIe port to ensure universal compatibility - it will not utilize the PCIe protocol but instead act as an alternative protocol to the same; one that is far more future proof and scalable than its archaic (soon-to-be) predecessor.

Déployer des mises à niveau importantes sur les capacités sur les ports existants est très impressionnant dans l'écosystème d'aujourd'hui et ce que Intel prétend n'est pas seulement une amélioration des petites capacités - c'est une amélioration massive.Le Cxl de première génération est conçu pour fonctionner sur PCIe Gen 5 (il est donc encore dans quelques années) et devrait accélérer le temps vers PCIe 6.Nous avons PCIe 3 depuis près de 8 ans maintenant et Intel s'apprête à raccourcir le cycle de mise à niveau de l'industrie pour cette norme.Le commutateur entre les protocoles PCIE et Cxl sera complètement transparent.

How Intel Cxl solves traditional PCIe Multi-GPU problems

La présentation qu'Intel a donnée aujourd'hui sur Cxl était axée sur l'aspect du centre de données de tout cela, mais nous voyons un angle beaucoup plus intéressant pour notre base de lecteurs - celui que l'entreprise n'a pas explicitement déclaré mais est assez évident une fois que vous y réfléchissez. While Cxl is pitched as the ultimate scaling fabric to glue together CPUs and accelerators there is no reason it cannot be used to achieve a finally-decent implementation of multi-GPU.C'est ce sur quoi je vais me concentrer dans ma couverture de Cxl.Appelons-le: multi-gpu cohérent.

L'un des principaux problèmes avec la mise à l'échelle de la PCIe en ce moment est que tout appareil connecté via lui a un pool de mémoire isolé, une latence élevée en termes de communication processeur-processeur et un manque de cohérence dans tout le système.C'est pourquoi des entreprises comme NVIDIA et AMD ont historiquement dû innover du côté du logiciel avec toutes sortes de techniques multi-GPU comme le rendu à cadre séparé ou le rendu séquentiel.Les multiples GPU n'ont pas agi comme un tout cohérent - ils ont agi indépendamment et il a montré.Cxl vise à réparer tout cela.

Avec Intel Cxl, un pool de mémoire cohérent peut être créé et la latence réduite par un ordre de grandeur.L'ensemble du système agira comme un tout cohésif et se réduira beaucoup mieux.Cela signifie que si vous avez un système exécutant un Intel XE DGPU, vous pouvez en jeter un autre dans une fente de PCIe de rechange et il devrait évoluer de manière transparente.Il y a trois protocoles que Cxl introduit:

Cxl.IO, qui est un protocole IO, remplace PCIe, pour la découverte, la configuration, l'accès à l'enregistrement, les interruptions, etc.. Then you have Cxl.cache and Cxl.mémoire, qui sont celles qui nous intéressent principalement.Ces protocoles permettent aux appareils connectés d'accéder à la mémoire et au cache de manière cohérente.Sur le papier, ceci est conçu pour que le CPU accéde à l'accélérateur VRAM et à l'accélérateur pour accéder au cache CPU, mais je ne vois aucune raison pour que ces protocoles ne permettent pas également à plusieurs GPU pour accéder à des tampons de mémoire les uns des autres.

You know the pesky limitation of multi-GPU where the VRAM never added up? Well, Cxl.memory and Cxl.Le cache en conjonction doit résoudre ce. Intel has also stated that unlike other interconnects, Cxl is designed for low latency - which is perfect for the multi-GPU approach. It is unclear at this time whether we can implement timing through Cxl as well or whether that would still require 'syncing' connections like SLI bridges.

Intel's Cxl protocol is also asymmetric, which allows the system to not only accept accelerators (read: GPUs) but also allows coherent memory buffers as well as protocol inoperability.Non seulement cela, mais il s'agit d'une norme beaucoup plus ouverte - permettant aux processeurs non intellets d'adopter le protocole - ce qui est essentiel si Intel souhaite une large acceptation de ce protocole. Coherency bias in the Cxl protocol, unlike traditional protocols, means that the GPU in question does not have to stop at the processor while accessing memory, it can do so on its own, alleviating driver latency.

Bien sûr, GPUS Mis à part une seconde, cette approche est principalement en cours pour une configuration de centre de données, donc les configurations à plusieurs billets et le CCIX sont ce que cela cible à partir du go-go.À cause de cela, il y a aussi un flux de biais de l'hôte - donc si vous le souhaitez vraiment - vous pouvez toujours utiliser le flux plus ancien. Essentially, Intel is trying to create a heteregenous computing infrastructure that allows CPUs, GPUs, accelerators, FPGAs and pretty much anything that can go on a PCIe port to be glued togather as a cohesive whole.

The future: Intel Xe GPUs in Cxl Mode?

Intel a été assez serré sur les détails de ses ambitions XE GPU.Tout ce que nous savons, c'est qu'il sera évolutif. It is a fairly good bet that multi-GPU is going to be involved in some way. Either through Cxl or through an MCM implementation or even both! It is also anyone's guess whether Cxl mode for GPUs will make its way to the mainstream consumer segment for enthusiasts like us - but it is very much clear that it solves a lot of problems that originally made multi-GPU setups unfeasible.

Cela fait longtemps que l'innovation ne s'est pas produite dans la pile logicielle et les protocoles qui contrôlent le flux de données du GPU au processeur et ce serait formidable de voir ce ruissellement jusqu'au niveau du consommateur grand public. If Intel starts out with a singular Xe GPU, Cxl mode can give it the edge to compete with higher-end variants from AMD and NVIDIA - and change the name of the game completely in the process.

If Cxl can seamlessly scale GPUs, then the economics of the market would also change completely.Les gens pourraient d'abord acheter un GPU moins cher et ensuite en ajouter un autre s'ils veulent plus de puissance.Cela ajouterait beaucoup plus de flexibilité dans l'achat de décisions et même de soulager les remords des acheteurs dans une certaine mesure pour la classe de jeu. If Cxl mode trickles down to the consumer level anytime soon, then we might even see motherboard designs change drastically as multiple sockets and multiple GPUs become a feasible option.Inutile de dire que les choses vont devenir assez excitantes dans quelques années.