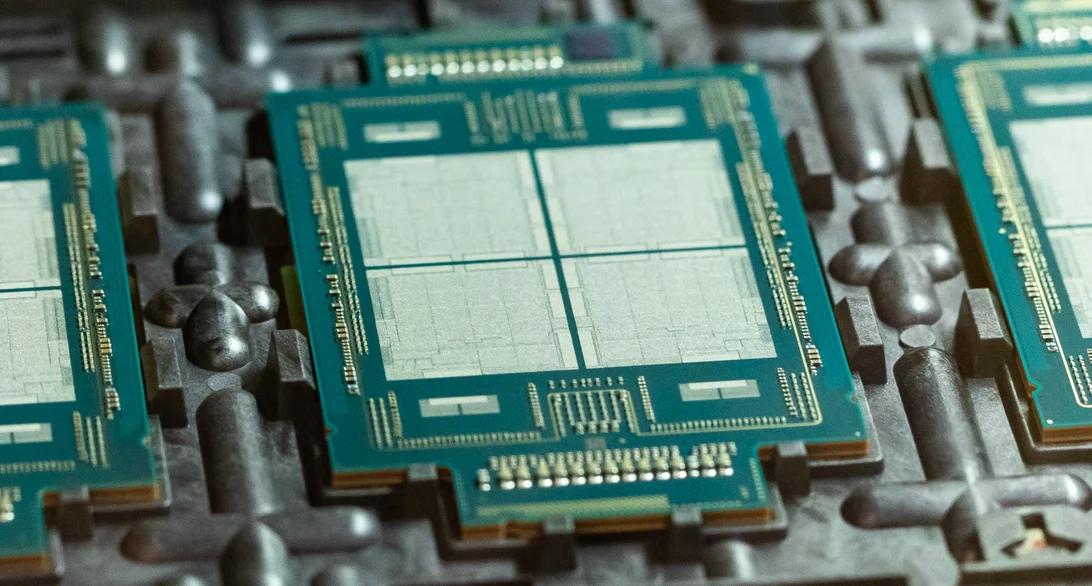

Une puce d'essai Intel Meteor Lake de Fab 42.(Crédits d'image: CNET)

CNET has managed to capture the first die shots of several next-generation Intel Meteor Lake CPUs, Sapphire Rapids Xeons & Ponte Vecchio GPUs that are being tested & produced inside the chipmaker's Fab 42, situated in Arizona, US.

Glorious Die Shots of Intel's Next-Gen Meteor Lake CPUs, Sapphire Rapids Xeons & Ponte Vecchio GPUs Captured at Fab 42 in Arizona

Les coups de vie ont été capturés par le journaliste principal de CNET, Stephen Shankland, qui a visité le Fab 42 d'Intel, situé en Arizona, aux États-Unis.Toute la magie se passe ici alors que l'usine de fabrication produit des puces de nouvelle génération pour les consommateurs, les centres de données et les segments informatiques hautes performances.Le Fab 42 gérera les puces de nouvelle génération d'Intel produites sur les nœuds de processus 10 nm (Intel 7) et 7nm (Intel 4).Certains des produits clés qui utiliseront ces nœuds de nouvelle génération comprennent les processeurs clients de Meteor Lake, les processeurs Sapphire Rapids Xeon et les GPU de Ponte Vecchio pour HPC.

Les processeurs AMD Ryzen 7000 pourraient avoir un avantage sur les capacités de mémoire Raptor Lake DDR5 d'Intel comme des vitesses «natives» de 5200 Mbps répertoriées pour la 13e génération

Intel 4 Powered Meteor Lake CPUs For Client Computing

Le premier produit à parler est le lac Meteor.En direction des PC de bureau client en 2023, les processeurs Meteor Lake seront le premier véritable design multi-chiplet d'Intel.CNET a réussi à prendre des photos des premiers puces de test du lac Meteor qui ressemblent remarquablement similaires aux rendus qu'Intel a taquin.Le véhicule d'essai du lac Meteor illustré ci-dessus est utilisé pour s'assurer que la conception d'emballage Forveros fonctionne correctement et comme prévu.Les processeurs Meteor Lake utiliseront la technologie d'emballage d'Intel pour interconnecter les différents IP de base intégrés sur la puce.

Chips d'essai d'Intel Meteor Lake préparez Chipzilla pour la production finale de processeurs de noyau de nouvelle génération.(Crédits d'image: CNET)

La matrice a quatre chiplets qui sont connectés ensemble sur le même substrat.Sur la base de ce qu'Intel a montré dans leurs rendus, la matrice supérieure devrait être la tuile de calcul, la tuile moyenne devrait être la tuile SOC-LP et le dépérissement le plus inférieur devrait être le tuile GPU.Cependant, sur la base des tailles de matrice, cela ne se passe pas bien.La matrice du milieu pourrait être la principale tuile de calcul qui abrite les noyaux et le plus petit en dessous pourrait être la tuile SOC-LP qui comprend l'EI.La matrice le plus supérieure doit être le GPU tandis que le plus petit dir à côté pourrait être un cache séparé ou une autre tuile IO.C'est juste une pure spéculation pour l'instant car ce sont des puces de test et la conception finale peut finir par être différente.

Nous obtenons également un premier aperçu de la plaquette de puce de test du lac Meteor qui mesure 300 mm en diagonale.La plaquette comprend des puces de test qui sont des matrices factice, encore une fois pour s'assurer que les interconnexions sur la puce fonctionnent comme prévu.Intel a déjà obtenu la puissance pour sa tuile de processeur de calcul Meteor Lake afin que nous puissions nous attendre à ce que les puces finales soient produites par le 2e de 2022 pour le lancement en 2023.

Intel adds Arc GPU, Rocky Linux, & multi-GPU functionality support to oneVPL 2022.1

Here's Everything We Know About The 14th Gen Meteor Lake 7nm CPUs

Nous avons déjà obtenu des détails d'Intel tels que le fait que la gamme de dektop et de mobilité d'Intel d'Intel devrait être basée sur une nouvelle gamme d'architecture COVE Core.Ce serait connu sous le nom de «Redwood Cove» et sera basé sur un nœud de processus EUV 7 nm.Il est indiqué que la Redwood Cove est conçue à partir de zéro pour être un nœud agnostique, ce qui signifie qu'il peut être fabriqué à différents Fabs.Il existe des références mentionnées qui indiquent que TSMC est une sauvegarde ou même un fournisseur partiel pour les puces basées sur Redwood Cove.Cela pourrait nous dire pourquoi Intel indique plusieurs processus de fabrication pour la famille CPU.

Les processeurs du lac Meteor peuvent être la première génération de CPU à partir d'Intel à dire adieu à l'architecture d'interconnexion du bus d'anneau.Il y a aussi des rumeurs selon lesquelles le lac Meteor pourrait être un design entièrement emporté en 3D et pourrait utiliser une matrice d'E / S provenant d'un FAB externe (TSMC aperçu).Il est souligné qu'Intel utilisera officiellement sa technologie d'emballage Foveros sur le CPU pour interconnecter les différentes matrices sur la puce (XPU).Cela s'aligne également avec Intel faisant référence à chaque tuile sur les puces de 14e génération individuellement (calcul des carreaux = cœurs CPU).

The Meteor Lake Desktop CPU family is expected to retain support on the LGA 1700 socket which is the same socket used by Alder Lake & Raptor Lake processors.Nous pouvons nous attendre à une mémoire DDR5 et à PCIe Gen 5.0 Support. The platform will support both DDR5 & DDR4 memory with the mainstream and budget tier options going for DDR4 memory DIMMs while the premium & high-end offerings going for DDR5 DIMMs.Le site répertorie également les processeurs Meteor Lake P et Meteor Lake M qui seront destinés aux plates-formes de mobilité.

Comparaison des générations de CPU de bureau Intel Mainstream.

| Intel CPU Family | Processor Process | Processors Cores/Threads (Max) | TDPs | Platform Chipset | Platform | Memory Support | PCIe Support | Launch |

|---|---|---|---|---|---|---|---|---|

| Sandy Bridge (2nd Gen) | 32nm | 4/8 | 35-95W | 6-Series | LGA 1155 | DDR3 | PCIe Gen 2.0 | 2011 |

| Ivy Bridge (3rd Gen) | 22nm | 4/8 | 35-77W | 7-Series | LGA 1155 | DDR3 | PCIe Gen 3.0 | 2012 |

| Haswell (4th Gen) | 22nm | 4/8 | 35-84W | 8-Series | LGA 1150 | DDR3 | PCIe Gen 3.0 | 2013-2014 |

| Broadwell (5th Gen) | 14nm | 4/8 | 65-65W | 9-Series | LGA 1150 | DDR3 | PCIe Gen 3.0 | 2015 |

| Skylake (6th Gen) | 14nm | 4/8 | 35-91W | 100-Series | LGA 1151 | DDR4 | PCIe Gen 3.0 | 2015 |

| Kaby Lake (7th Gen) | 14nm | 4/8 | 35-91W | 200-Series | LGA 1151 | DDR4 | PCIe Gen 3.0 | 2017 |

| Coffee Lake (8th Gen) | 14nm | 6/12 | 35-95W | 300-Series | LGA 1151 | DDR4 | PCIe Gen 3.0 | 2017 |

| Coffee Lake (9th Gen) | 14nm | 8/16 | 35-95W | 300-Series | LGA 1151 | DDR4 | PCIe Gen 3.0 | 2018 |

| Comet Lake (10th Gen) | 14nm | 10/20 | 35-125W | 400-Series | LGA 1200 | DDR4 | PCIe Gen 3.0 | 2020 |

| Rocket Lake (11th Gen) | 14nm | 8/16 | 35-125W | 500-Series | LGA 1200 | DDR4 | PCIe Gen 4.0 | 2021 |

| Alder Lake (12th Gen) | Intel 7 | 16/24 | 35-125W | 600 Series | LGA 1700 | DDR5 / DDR4 | PCIe Gen 5.0 | 2021 |

| Raptor Lake (13th Gen) | Intel 7 | 24/32 | 35-125W | 700-Series | LGA 1700 | DDR5 / DDR4 | PCIe Gen 5.0 | 2022 |

| Meteor Lake (14th Gen) | Intel 4 | TBA | 35-125W | 800 Series? | TBA | DDR5 | PCIe Gen 5.0? | 2023 |

| Arrow Lake (15th Gen) | Intel 20A | 40/48 | TBA | 900-Series? | TBA | DDR5 | PCIe Gen 5.0? | 2024 |

| Lunar Lake (16th Gen) | Intel 18A | TBA | TBA | 1000-Series? | TBA | DDR5 | PCIe Gen 5.0? | 2025 |

| Nova Lake (17th Gen) | Intel 18A | TBA | TBA | 2000-Series? | TBA | DDR5? | PCIe Gen 6.0? | 2026 |

Intel 7 Powered Sapphire Rapids CPUs For Xeon Data Center & Servers

Nous obtenons également un aperçu plus détaillé du substrat Intel Sapphire Rapids-Sp Xeon CPU, des chiplets et de la conception complète des emballages (variantes standard et HBM).La variante standard comprend quatre tuiles qui incorporeront les chiplets de calcul.Il y a aussi quatre pin-off pour les packages HBM.La puce communiquera avec les 8 chiplets (quatre calculs / quatre hbm) via des interconnexions EMIB qui sont les plus petites barres rectangulaires sur le bord de chaque dé.

A substrate of the Intel Sapphire Rapids-SP Xeon CPU with HBM2e memory.(Crédits d'image: CNET)Le produit final peut être vu ci-dessous et montre les quatre carreaux de calcul Xeon au milieu avec quatre petits packages HBM2 sur les côtés.Intel a récemment confirmé que ses processeurs Sapphire Rapids-Sp Xeon comporteront jusqu'à 64 Go de mémoire HBM2E à bord des CPU.Il s'agit de la conception du processeur à part entière illustrée ici et montre qu'elle est prête pour le déploiement dans les centres de données de nouvelle génération d'ici 2022.

The final 4th Gen Sapphire Rapids-SP Xeon CPU with its multi-chiplet design housing Compute & HBM2e tiles.(Crédits d'image: CNET)Here's Everything We Know About The 4th Gen Intel Sapphire Rapids-SP Xeon Family

Selon Intel, le Sapphire Rapids-SP sera disponible en deux variantes de package, une norme et une configuration HBM.La variante standard comportera une conception chiplet composée de quatre matrices XCC qui comporteront une taille de matrice d'environ 400 mm2.Ceci est la taille de la matrice pour une matrice XCC singulière et il y en aura quatre au total sur le haut Sapphire Rapids-Sp Xeon Chip.Chaque mat sera interconnecté via EMIB qui a une taille de pas de 55U et un pas de base de 100U.

La puce Xeon standard Sapphire Rapids-Sp comportera 10 interconnexions EMIB et l'ensemble se mesurera à un puissant 4446 mm2.En passant à la variante HBM, nous obtenons un nombre accru d'interconnexions qui se trouvent à 14 et sont nécessaires pour interconnecter la mémoire HBM2E aux noyaux.

Les quatre packages de mémoire HBM2E comporteront des piles de 8 Hi, donc Intel va pour au moins 16 Go de mémoire HBM2E par pile pour un total de 64 Go sur le package Sapphire Rapids-Sp.En parlant de l'emballage, la variante HBM mesurera à un fou 5700 mm2 ou 28% plus grand que la variante standard.Comparé aux nombres EPYC GenoA récemment divulgués, le package HBM2E pour Sapphire Rapids-SP finirait par 5% plus grand tandis que le package standard sera 22% plus petit.

Intel indique également que la liaison EMIB offre deux fois l'amélioration de la densité de bande passante et 4 fois une meilleure efficacité énergétique par rapport aux conceptions de packages standard.Fait intéressant, Intel appelle la dernière gamme Xeon logiquement monolithique, ce qui signifie qu'ils font référence à l'interconnexion qui offrira les mêmes fonctionnalités qu'une seule die, mais techniquement, il y a quatre chiplets qui seront interconnectés ensemble. You can read the full details regarding the standard 56 core & 112 thread Sapphire Rapids-SP Xeon CPUs here.

Familles Intel Xeon Sp (préliminaire):

| Family Branding | Skylake-SP | Cascade Lake-SP/AP | Cooper Lake-SP | Ice Lake-SP | Sapphire Rapids | Emerald Rapids | Granite Rapids | Diamond Rapids |

|---|---|---|---|---|---|---|---|---|

| Process Node | 14nm+ | 14nm++ | 14nm++ | 10nm+ | Intel 7 | Intel 7 | Intel 3 | Intel 3? |

| Platform Name | Intel Purley | Intel Purley | Intel Cedar Island | Intel Whitley | Intel Eagle Stream | Intel Eagle Stream | Intel Mountain Stream Intel Birch Stream | Intel Mountain Stream Intel Birch Stream |

| Core Architecture | Skylake | Cascade Lake | Cascade Lake | Sunny Cove | Golden Cove | Raptor Cove | Redwood Cove? | Lion Cove? |

| IPC Improvement (Vs Prev Gen) | 10% | 0% | 0% | 20% | 19% | 8%? | 35%? | 39%? |

| MCP (Multi-Chip Package) SKUs | No | Yes | No | No | Yes | Yes | TBD (Possibly Yes) | TBD (Possibly Yes) |

| Socket | LGA 3647 | LGA 3647 | LGA 4189 | LGA 4189 | LGA 4677 | LGA 4677 | TBD | TBD |

| Max Core Count | Up To 28 | Up To 28 | Up To 28 | Up To 40 | Up To 56 | Up To 64? | Up To 120? | Up To 144? |

| Max Thread Count | Up To 56 | Up To 56 | Up To 56 | Up To 80 | Up To 112 | Up To 128? | Up To 240? | Up To 288? |

| Max L3 Cache | 38.5 MB L3 | 38.5 MB L3 | 38.5 MB L3 | 60 MB L3 | 105 MB L3 | 120 MB L3? | 240 MB L3? | 288 MB L3? |

| Vector Engines | AVX-512/FMA2 | AVX-512/FMA2 | AVX-512/FMA2 | AVX-512/FMA2 | AVX-512/FMA2 | AVX-512/FMA2 | AVX-1024/FMA3? | AVX-1024/FMA3? |

| Memory Support | DDR4-2666 6-Channel | DDR4-2933 6-Channel | Up To 6-Channel DDR4-3200 | Up To 8-Channel DDR4-3200 | Up To 8-Channel DDR5-4800 | Up To 8-Channel DDR5-5600? | Up To 12-Channel DDR5-6400? | Up To 12-Channel DDR6-7200? |

| PCIe Gen Support | PCIe 3.0 (48 Lanes) | PCIe 3.0 (48 Lanes) | PCIe 3.0 (48 Lanes) | PCIe 4.0 (64 Lanes) | PCIe 5.0 (80 lanes) | PCIe 5.0 (80 Lanes) | PCIe 6.0 (128 Lanes)? | PCIe 6.0 (128 Lanes)? |

| TDP Range (PL1) | 140W-205W | 165W-205W | 150W-250W | 105-270W | Up To 350W | Up To 375W? | Up To 400W? | Up To 425W? |

| 3D Xpoint Optane DIMM | N/A | Apache Pass | Barlow Pass | Barlow Pass | Crow Pass | Crow Pass? | Donahue Pass? | Donahue Pass? |

| Competition | AMD EPYC Naples 14nm | AMD EPYC Rome 7nm | AMD EPYC Rome 7nm | AMD EPYC Milan 7nm+ | AMD EPYC Genoa ~5nm | AMD Next-Gen EPYC (Post Genoa) | AMD Next-Gen EPYC (Post Genoa) | AMD Next-Gen EPYC (Post Genoa) |

| Launch | 2017 | 2018 | 2020 | 2021 | 2022 | 2023? | 2024? | 2025? |

Intel 7 Powered Ponte Vecchio GPUs For HPC

Enfin, nous avons une vue magnifique sur le GPU Intel Ponte Vecchio, la solution HPC de nouvelle génération.Ponte Vecchio a été conçu et créé sous la direction de Raja Koduri qui nous a fourni de grandes friandises concernant la philosophie de conception et la puissance de calcul folle que cette puce contient.

Intel's Ponte Vecchio is a gold mine of chiplets, housing over 47 different tiles on the same package.(Crédits d'image: CNET)Here's Everything We Know About The Intel 7 Powered Ponte Vecchio GPUs

En se déplaçant vers Ponte Vecchio, Intel a décrit certaines caractéristiques clés de son GPU de centre de données phares telles que 128 cœurs Xe, 128 unités RT, la mémoire HBM2E et un total de 8 GPU XE-HPC qui seront connectés ensemble.La puce comportera jusqu'à 408 Mo de cache L2 dans deux piles distinctes qui se connecteront via l'interconnexion EMIB.La puce comportera plusieurs matrices basées sur le processus `` Intel 7 '' d'Intel et les nœuds de processus N7 / N5 de TSMC.

Intel a également détaillé le package et la taille de la taille de son GPU phare Ponte Vecchio basé sur l'architecture Xe-HPC.La puce sera composée de 2 carreaux avec 16 matrices actives par pile.La taille maximale active de la matrice supérieure sera de 41 mm2 tandis que la taille de base de base qui est également appelée «carreau de calcul» se trouve à 650 mm2.Nous avons tous les chiplets et les nœuds de processus que les GPU Ponte Vecchio utiliseront, énumérés ci-dessous:

Voici comment Intel atteint 47 tuiles sur la puce Ponte Vecchio:

Le GPU Ponte Vecchio utilise 8 piles Hbm 8 Hi et contient un total de 11 interconnexions EMIB.L'ensemble du paquet Intel Ponte Vecchio mesurerait 4843.75 mm2.Il est également mentionné que le pas de bosse pour les processeurs de lac Meteor à l'aide de l'emballage 3D Forveros à haute densité sera 36U.

The Ponte Vecchio GPU will be competing against NVIDIA and AMD HPC GPUs in 2022.(Crédits d'image: CNET)Le GPU Ponte Vecchio n'est pas 1 puce mais une combinaison de plusieurs puces.C'est une centrale chiplet, emballant le plus de chiplets sur n'importe quel GPU / CPU, 47 pour être précis.Et ceux-ci ne sont pas basés sur un seul nœud de processus mais plusieurs nœuds de processus car nous avions détaillé quelques jours en arrière.

Accélérateurs du GPU du centre de données de nouvelle génération

| GPU Name | AMD Instinct MI250X | NVIDIA Hopper GH100 | Intel Ponte Vecchio |

|---|---|---|---|

| Packaging Design | MCM (Infinity Fabric) | Monolithic | MCM (EMIB + Foveros) |

| GPU Architecture | Aldebaran (CDNA 2) | Hopper GH100 | Xe-HPC |

| GPU Process Node | 6nm | 4N | 7nm (Intel 4) |

| GPU Cores | 14,080 | 16,896 | 16,384 ALUs (128 Xe Cores) |

| GPU Clock Speed | 1700 MHz | ~1780 MHz | TBA |

| L2 / L3 Cache | 2 x 8 MB | 50 MB | 2 x 204 MB |

| FP16 Compute | 383 TOPs | 2000 TFLOPs | TBA |

| FP32 Compute | 95.7 TFLOPs | 1000 TFLOPs | ~45 TFLOPs (A0 Silicon) |

| FP64 Compute | 47.9 TFLOPs | 60 TFLOPs | TBA |

| Memory Capacity | 128 GB HBM2E | 80 GB HBM3 | 128 GB HBM2e |

| Memory Clock | 3.2 Gbps | 3.2 Gbps | TBA |

| Memory Bus | 8192-bit | 5120-bit | 8192-bit |

| Memory Bandwidth | 3.2 TB/s | 3.0 TB/s | ~3 TB/s |

| Form Factor | OAM | OAM | OAM |

| Cooling | Passive Cooling Liquid Cooling | Passive Cooling Liquid Cooling | Passive Cooling Liquid Cooling |

| TDP | 560W | 700W | TBD |

| Launch | Q4 2021 | 2H 2022 | 2022? |

Le Fab 42 d'Intel devrait bientôt fusionner avec le prochain Fab 52 et Fab 62 dans les prochaines années qui produiront ce qui vient ensuite.Le PDG d'Intel, Pat Gelsinger, a déjà inauguré les Fabs en septembre et c'est là que vous verrez la production des produits Sous-Intel 7 de Next Gen.

Feuille de route Intel Process

| Process Name | Intel 10nm SuperFin | Intel 7 | Intel 4 | Intel 3 | Intel 20A | Intel 18A |

|---|---|---|---|---|---|---|

| Production | In High-Volume (Now) | In Volume (Now) | 2H 2022 | 2H 2023 | 2H 2024 | 2H 2025 |

| Perf/Watt (over 10nm ESF) | N/A | 10-15% | 20% | 18% | >20%? | TBA |

| EUV | N/A | N/A | Yes | Yes | Yes | High-NA EUV |

| Transistor Architecture | FinFET | Optimized FinFET | Optimized FinFET | Optimized FinFET | RibbonFET | Optimized RibbonFET |

| Products | Tiger Lake | Alder Lake Raptor Lake Sapphire Rapids Emerald Rapids Xe-HPG? | Meteor Lake Xe-HPC / Xe-HP? | Granite Rapids Sierra Forest TBA | Arrow Lake Diamond Rapids? TBA | Lunar Lake Nova Lake TBA TBA |

Source des nouvelles: CNET