La mise à l'échelle du transistor atteint un point de basculement à 3 nm, où les FET nanoches remplaceront probablement les FINFET pour atteindre les performances, la puissance, la zone et le coût (PPAC).Un changement architectural significatif est également évalué pour les interconnexions en cuivre à 2 nm, une décision qui reconfigurerait la façon dont la puissance est délivrée aux transistors.

Cette approche repose sur les soi-disant rails de puissance (BPR) et la distribution de puissance arrière, laissant les interconnexions frontales pour transporter des signaux.Intel a annoncé qu'il utiliserait sa structure Powervia à sa génération de 20Å (équivalent 2 nm), et d'autres fabricants de puces évaluent des schémas similaires.

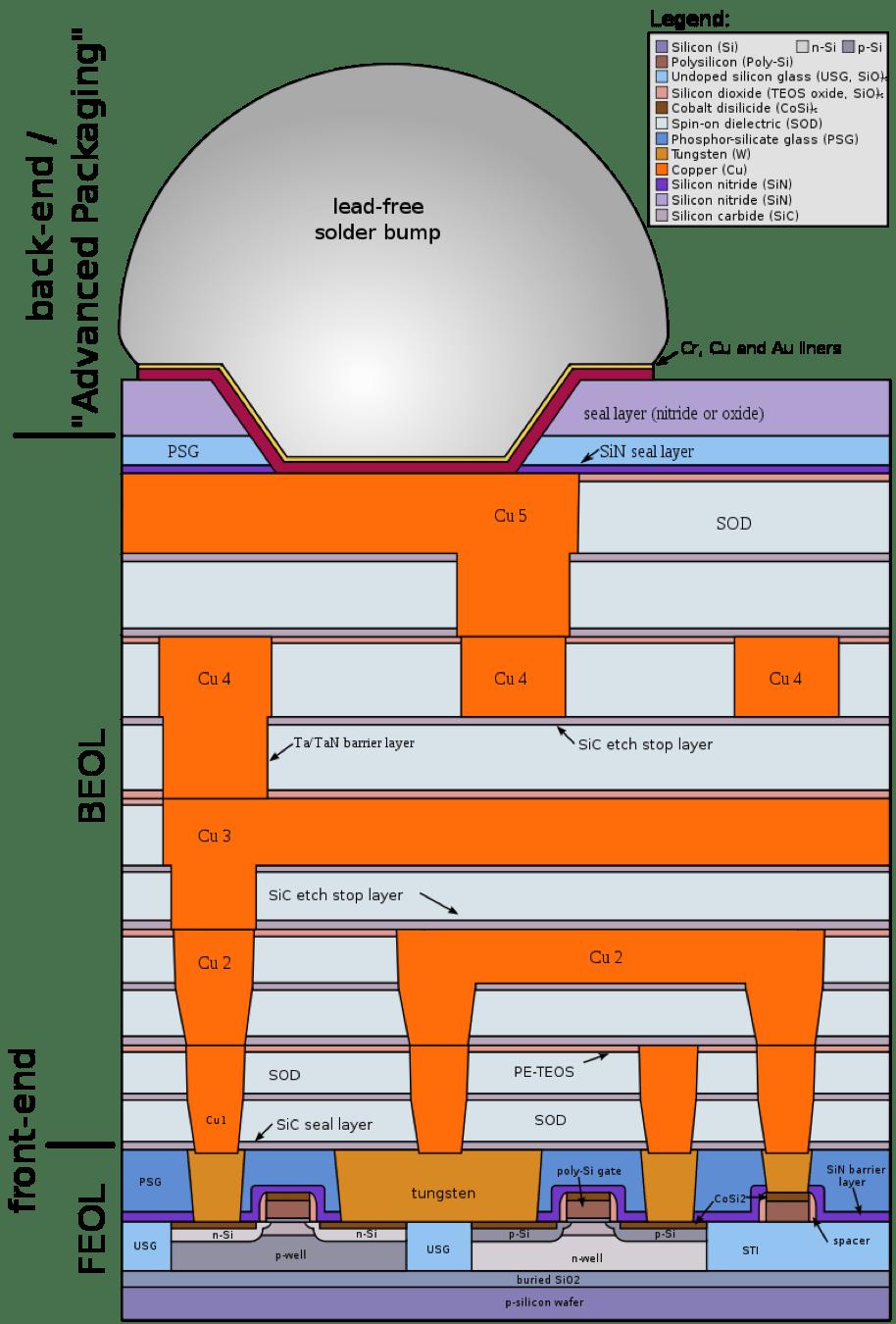

Les fabricants de puces devraient également remplacer le cuivre à certains niveaux par du ruthénium ou du molybdène dès le nœud 2 nm.D'autres changements plus modestes étendront les interconnexions de cuivre de Damasnee en utilisant une faible résistance via des processus, des revêtements alternatifs et entièrement aligné via des approches.

Une grande partie de l'optimisation se produit autour des liens faibles de la chaîne - le contact (métal 0), le métal 1 et les vias, où les retards RC sont les plus susceptibles de ralentir la puce."Pour via le remplissage, le dépôt conforme de barrière, de graines et de métal via peut être supplanté par un dépôt sans barrière et un remplissage ascendante de cobalt, et peut-être même du ruthénium", a déclaré Ajit Paranjpe, CTO de Veeco.

Les défis d'interconnexion commencent à la lithographie, où l'EUV est employé tout au long du processus 5 nm, contribuant de manière significative au coût.

EUV and BEOL patterning

Only a handful of mask levels require EUV lithography at the 7nm node, but this changes to between 15 and 18 levels at 5nm (about 30nm metal pitch).Dans la lithographie, une préoccupation croissante est les erreurs de placement de bord (EPES) en raison de fonctionnalités à impréurs.Robert Socha, un boursier ASML, a souligné la nécessité de contrôler et de réduire les contributeurs à EPES au nœud 5 nm.Un contributeur critique est des erreurs de superposition, avec un budget de superposition de seulement 2.5 nm (5 atomes de silicium de large) au nœud 5 nm.

«Nous avons vu l'élément de superposition du budget EPE rétrécir le plus rapide avec une variation plus élevée dans le champ», a déclaré Andrew Cross, directeur des solutions de contrôle des processus chez KLA.«Cela conduit à un échantillonnage de superposition optique plus élevé, à une amélioration des techniques de mesure de la superposition et à l'utilisation de mesures de superposition à base de SEM après le développement de résister et après la gravure, ce qui appelle à la synergie entre les outils optiques et les outils en ligne."

Via optimization

A key strategy in extending copper technology involves eliminating the barrier metal, TaN, at the copper via bottom.Cela peut être accompli en déposant sélectivement un film monocouche (SAM) auto-assemblé, en déposant le bronzage par dépôt de couche atomique (ALD) le long des parois latérales, et enfin en supprimant le SAM et en remplissant du cuivre.À l'IITC, Tel a décrit un tel processus en utilisant une double intégration de Damascène [1] et en comparant deux monocouches auto-assemblées (A et B).Après la barrière de bronzage ALD, les SAM ont été évaporés, suivis d'un dépôt électrolytique en cuivre (ELD) dans le VIA (voir figure 1).Après via le préfilé, une doublure de ruthénium a été déposée par CVD sur les parois de tranchée, suivie d'un remplissage PVD ionisé en cuivre.Avec SAM B, les résultats n'ont montré pas de TA (EDX) en bas via.Un aspect clé de tout SAM est qu'il peut résister à la température du processus de l'ALD, qui est d'environ 350 ° C.

Les fabricants de puces se tournent de plus en plus vers les processus SAM, que ce soit par CVD ou Spin-Coat, comme essentiel à la réduction de la résistance globale et à l'extension des processus de damascène en cuivre au nœud 2 nm.

Une autre stratégie qui réduit le volume du métal barrière (tan) au fond via implique une transition du Tan PVD à Ald Tan, qui est plus conforme et se traduit par un film plus mince et plus continu.Ald Tan devrait être largement mis en œuvre au nœud 5 nm, peut-être avec les processus SAM.

figue.1: Dans ce processus de monocouche auto-assemblé (SAM), un film masque le Bia Bottom pendant l'ald de la barrière et les graines de cuivre.Le SAM est ensuite retiré par vaporisation à 325 ° C, suivi d'un remplissage de cuivre.Source: Tel / IITC

Fully aligned vias, selective deposition

The idea behind fully aligned vias (FAVs) is to reduce the impact of edge placement errors between vias and lines, which lead to device failures and long-term reliability issues.Depuis le nœud 32 nm, les fabricants de puces utilisent des méthodes auto-alignées en utilisant des masques durs en étain pour aligner les interconnexions au niveau ci-dessous.Dans des vias entièrement alignés, la via inférieur et ci-dessus est enregistré.Il existe deux méthodes pour réaliser des faves, en gravant du cuivre à partir des lignes ci-dessous, puis en motivant et en déposant la via, ou en déposant un film diélectrique sélectivement sur le diélectrique à faible K, suivi de la structuration via.

Les ingénieurs d'IBM et Lam Research ont présenté une approche entièrement alignée utilise un dépôt diélectrique sélectif dans un processus global simplifié [2].Selon le groupe, l'intégration FAV peut permettre une résistance inférieure à 70% et une augmentation de 30% dans la zone de contact tout en maintenant la fiabilité de la via-ligne (voir figure 2).En utilisant des structures d'essai de 32 nm-pitch de cuivre et de diélectrique à faible k (SICOH), l'équipe a utilisé une chimie humide pour recueillir le cuivre, la doublure et la barrière.

“[The recess etch], when combined with an etch-selective dielectric cap, acts as a via guiding pattern, mitigating overlay and critical dimension (CD) induced edge placement errors," according to IBM.Un film sélectif d'oxyde d'aluminium a été déposé par CVD sur le bas et agit comme un arrêt de gravure partiel.La clé du succès du processus est une sélectivité élevée avec une prolifération latérale limitée du film diélectrique, et aucune diminution ni variation de résistance par rapport à son processus FAV standard.IBM a déclaré qu'un autre avantage est le rapport d'aspect inférieur des lignes métalliques (car la récréation est peu profonde), ce qui assouplit le remplissage du cuivre.

À l'heure. “The question is in what form — at what levels and at what pitch will (fully aligned vias) be required?" asks Zsolt Tokei, an Imec fellow.Il a noté que même si les approches de gravure de la récréation et de dépôt sélectif ont leurs avantages et leurs inconvénients, le problème clé est la défectivité et augmenter le rendement sur de nouveaux processus.Même ainsi, avec la tolérance EPE toujours plus pas plus passante aux nœuds 3 nm et 2 nm, les approches comme Fav deviendront probablement plus convaincantes.

figue.2: Un processus de dépôt sélectif a été utilisé pour fabriquer un niveau à deux niveaux entièrement aligné via pour un nœud de 5 nm.Source: IBM / IITC

Le dépôt sélectif, également connu sous le nom de dépôt sélectif de la zone (TSA), existe depuis des décennies, mais ce n'est que ces dernières années qu'il a fait le pas du laboratoire à Fab. For ASD, the “killer app" proved to be deposition of cobalt caps on copper lines, which enables superior control of electromigration over traditional silicon nitride caps.Cette technique a été adoptée par certaines entreprises du nœud 10 nm.Avec une doublure en cobalt sous le cuivre (les doublures sont également appelées couches de nucléation ou couches de colle car elles permettent une adhésion en métal), le cobalt encadre le cuivre dans ce schéma.

Les processus ALD sélectifs fonctionnent mieux lorsque l'objectif est de déposer du métal sur le métal ou de diélectrique sur diélectrique.Selon le fournisseur d'équipement, différents mécanismes chimiques peuvent être utilisés pour garder le dépôt sélectif et empêcher le dépôt où il n'est pas recherché.Pour la métallisation des contacts, le dépôt sélectif du tungstène réduit considérablement la résistivité grâce à une meilleure garniture et potentiellement éliminer complètement la barrière d'étain (voir figure 3).En éliminant les barrières et les doublures, le tungstène sélectif permet également une interface métal-métal propre pour une résistance globale plus faible.Selon Applied Materials, une réduction de 40% de la résistance est possible.

figue.3: Le remplissage sélectif de tungstène ascendant fournit une voie pour éliminer les couches de barrière et de doublure, améliorant le contact et la résistance.Source: Matériaux appliqués

Cobalt and tungsten

Up until the 14nm or 10nm technology node, tungsten has remained the mainstay for making electrical contact to the metal/polysilicon gate and the source and drain silicide regions on transistors.Ces dernières années, des contacts de cobalt ont été adoptés avec une fine barrière d'étain.De même dans les lignes ou les vias, la barrière plus mince, ainsi que le libre parcours moyen du cobalt (10 nm vs.39 nm pour le cuivre), entraîne une résistivité plus faible dans les petits fils (avec un chemin électronique plus long, la diffusion augmente la résistance nette).

Intel a été la première entreprise à utiliser Cobalt en production au niveau de contact, et en fait les problèmes d'intégration avec Cobalt peuvent avoir été une cause partielle de problèmes avec les retards de 10 nm d'Intel.Néanmoins, plusieurs fabricants de puces ont fait la transition vers l'utilisation de cobalt dans les processus de production pour les contacts, mais aussi comme une doublure et un matériau de plafonnement dans les interconnexions en cuivre.

Le métal de revêtement affecte de manière critique la qualité de remplissage du cuivre dans les lignes d'interconnexion à l'échelle.Dans une présentation invitée à l'IITC, l'IBM a démontré des performances d'électromigration améliorées en utilisant une nouvelle doublure, ruthénium dopé au cobalt par CVD [3], par rapport aux revêtements de ruthénium CVD COBALT et CVD dans des structures métalliques 36 nm.IBM a déterminé que la nouvelle doublure donne une meilleure résistance aux EM car le cobalt dans la doublure de ruthénium supprime la diffusion le long des joints de grains causés par le capuchon de cobalt sur le cuivre.Le cuivre PVD avec reflux à basses températures (250 ° C) devient courant pour les interconnexions denses, tandis que le cuivre ou le DPE électrolaires sont utilisés à des niveaux globaux.

The next metal: Ru or Mo?

It appears that at the 1nm node (20nm metal pitch), a change from copper to an alternative metal —ruthenium or molybdenum — will become necessary, at least for some levels.Fait intéressant, le molybdène et le ruthénium sont explorés comme remplacements de ligne de mots pour le tungstène dans les transistors Flash Nand 3D.

Pour le choix de l'industrie de remplacer le cuivre, la résistance aux caractéristiques à l'échelle est la métrique primordiale.La résistance EM est également liée à la fiabilité à long terme.Une grande partie de l'avantage du ruthénium, du molybdène et du cobalt est le potentiel d'éliminer les revêtements, offrant plus de tranchées ou de volume à être occupées par le métal principal.Un recuit de reflux ou de laser peut être utilisé pour maximiser la taille des grains.

«Pour les lignes métalliques, le ruthénium est un remplacement probable. While the bulk resistivity of ruthenium is 7 µohm-cm, the effective resistivity of a 20nm ruthenium film deposited with traditional sputtering is >11 µohm-cm," said Veeco’s Paranjpe.«Ainsi, des méthodes alternatives telles que le dépôt de faisceau d'ions, qui offre un plus grand contrôle sur la texture cristalline et la taille des grains, sont en cours d'exploration."

Le ruthénium est attrayant en tant qu'interconnexion de nouvelle génération en raison de sa faible résistivité, de son point de fusion élevé, de sa résistance à l'attaque des acides et de son potentiel extrêmement faible de corrosion.

Les précurseurs de molybdène, en revanche, sont un ordre de grandeur moins cher que le ruthénium.Ni l'un ni l'autre ne sera nécessaire avant le nœud 2 nm.

“Molybdenum is definitely cheaper, so if you’re a fab manager you will be happier," said Imec’s Tokei."Mais si vous êtes ingénieur, vous devez avoir toutes les données disponibles pour prendre une décision entre les matériaux, et nous n'avons pas encore de jeu de données complet."

figue.4: En construisant un rail de la région d'isolement du transistor à travers la tranche de silicium, la livraison de puissance du transistor (arrière) est séparée de la livraison du signal (Frontside).Source: IMEC

Buried power rails

The combination of BPR and backside power distribution (BPD) essentially takes power and ground wires, which previously were routed through the entire multi-level metal interconnect, and gives these a dedicated network on the wafer backside (see figure 4).Cela réduit la tension (IR) goutte.

«Dans l'interconnexion conventionnelle, vous devez optimiser sur le métal 0 et le métal 1 pour la puissance et les signaux, de sorte que la puissance entraîne une grande interconnexion et le signal entraîne une interconnexion maigre. You end up with a tradeoff, which is not optimal for either," explained Tokei.«En achetant la puissance vers l'arrière, il y aura des interconnexions hautes et relativement larges, et vous vous retrouvez avec un signal et une horloge sur le devant avec des lignes relativement maigres et résistives, et vous gagnez considérablement." He noted that thermal management is being evaluated carefully for these new structures.

De nombreux défis existent concernant les BPR et les BPD, y compris la façon de construire le rail d'alimentation enterré, comment connecter le réseau de distribution d'alimentation au rail de puissance et comment transférer l'alimentation du rail de puissance au transistor.Ces décisions détermineront les schémas d'intégration et la puissance ultime et les gains de mise à l'échelle.

Mehul Naik, directrice générale du développement avancé des technologies des produits chez Applied Materials, a déclaré que les défis de fabrication varieront, selon le schéma, et peuvent inclure des remplissages métalliques à haut rendement, des choix métalliques et diélectriques, et de l'amincissement à la plaque à travers le broyage arrière et le CMP,entre autres.

Intel a annoncé qu'il utiliserait son Powervia à sa génération de 20Å (2 nm), qu'il vise à avoir en production à haut volume en 2024.Semiconductor Engineering a discuté de Powervia avec Ann Kelleher d'Intel, vice-présidente principale et directrice générale du développement technologique, et a demandé en quoi il différait des autres approches en cours de développement. “Buried power rail, at the highest level, is the same general theme," Kelleher said."Cependant, cela diffère dans la façon dont il est réalisé.Nous livrons la puissance de l'arrière de la tranche au transistor.Buried Power Rail est essentiellement l'obtient de l'avant, vous avez donc une architecture différente pour réaliser cela.C'est la différence clé."

Notamment, Powervia d'Intel semble se connecter aux contacts, tandis que le rail de puissance d'IMEC est intégré dans le STI (isolation de la tranchée peu profonde).

David Fried, vice-président des produits informatiques chez LAM Research, compare l'approche ferroviaire enterrée d'un sous-sol dans une maison. “If you use a basement analogy, there will need to be a stairwell on each side," he said.«Vous avez maintenant la possibilité d'accéder aux articles au rez-de-chaussée des deux côtés au lieu d'un seul.Cela peut ouvrir une toute nouvelle dimension de conception lorsque vous pouvez accéder aux transistors en dessous ou d'en haut.C'est un énorme changement."

Bien que ce passage à l'accès à la construction aux transistors sur la plaquette avant et arrière nécessitera de nombreuses innovations de processus et de conception, le fait que la puissance arrière aurait toujours une construction plane par niveau de niveau s'appuie sur le savoir-faire existant de l'industrie.

“This is one of the technologies I’m fairly optimistic about," said Fried."Ce sont les innovations difficiles et multiples, mais à la base, ils sont prouvés.Ainsi, un rail de puissance enterré n'est qu'un autre niveau bidimensionnel sur un flux tridimensionnel.C'est toujours un traitement plan.Le rassembler et le faire fonctionner est vraiment, vraiment difficile, mais à la base, il n'est pas aussi révolutionnaire que d'autres options."

Les innovations de processus dans la métallisation, les diélectriques et le CMP seront nécessaires. “When you take the power rail and connect it to the device, how do you make sure the interfaces are clean enough and how do you reduce power losses in that transfer? Pre-clean and integration with void-free low-resistivity metals will be very important," Applied Materials’ Naik said.«Des diélectriques budgétaires thermiques de haute qualité (≤400 ° C) seront nécessaires, car ces processus se produisent après que le dispositif frontal, y compris la métallisation, a été fabriqué."

Une autre clé est CMP.Pour l'amincissement des plaquettes, le broyage de la plaque arrière sera suivi par CMP pour éclaircir la plaquette de l'appareil. “From a yield perspective, it will be CMP’s job to make sure all incoming non-uniformity is managed to achieve the desired global wafer thickness uniformity at low defectivity," said Naik.

Du point de vue de l'éclairage de la plaquette, à la fois l'empilement multi-chip pour la mémoire HBM et maintenant la livraison de puissance arrière pour la logique, le trafiquant à 10 micron, mais il y a un intérêt énorme à s'arrêter.«L'empilement à haute densité entraîne ce besoin et les concepteurs veulent encore du silicium plus mince que ce qui est disponible aujourd'hui. From the moment something is needed, then technologists will extend the capability and that’s what is happening with chip stacking," said Tokei.

Conclusion

Chipmakers are evaluating many process changes for 5nm and beyond, including via resistance optimization, fully aligned vias, cobalt caps and contacts, and the separating of power and signal lines to free up congested interconnect layers.L'industrie des semi-conducteurs est toujours plus ouverte à la modification progressive des processus, plutôt qu'à de grands changements de matériaux et structurels, dans la mesure du possible.

De nouvelles revêtements qui améliorent la fiabilité, en supprimant la barrière des bas et des vias entièrement alignés, semblent permettre des solutions.Les ingénieurs commencent à résoudre les défis concernant les rails d'alimentation et le traitement arrière.Le dépôt sélectif est entré dans des Fabs pour les bouchons de cobalt et gagnera probablement l'acceptation dans des applications supplémentaires à l'avenir.

Les références

Related Stories

Inside Intel’s Ambitious Roadmap

Five process nodes in four years, high-NA EUV, 3D-ICs, chiplets, hybrid bonding, and more.

Breaking the 2nm Barrier

New interconnects and processes will be required to reach the next process nodes.