Expertos en la mesa: la ingeniería de semiconductores se sentó para discutir las condiciones económicas y cómo eso afecta el diseño de chips con Anirudh Devgan, presidente y CEO de Cadence;Joseph Sawicki, vicepresidente ejecutivo de Siemens EDA;Niels Faché, vicepresidente y gerente general de Keysight;Simon Segars, asesor en el brazo;y Aki Fujimura, presidente y CEO de D2S.Esta discusión se llevó a cabo frente a una audiencia en vivo en el reciente evento de diseño de sistemas electrónicos..Lo que sigue son extractos de esa discusión.Para ver la primera parte, haga clic aquí.

SE: ¿Solíamos pensar que EDA era a prueba de recesión porque el diseño siempre continúa durante una recesión?¿Sigue siendo cierto?

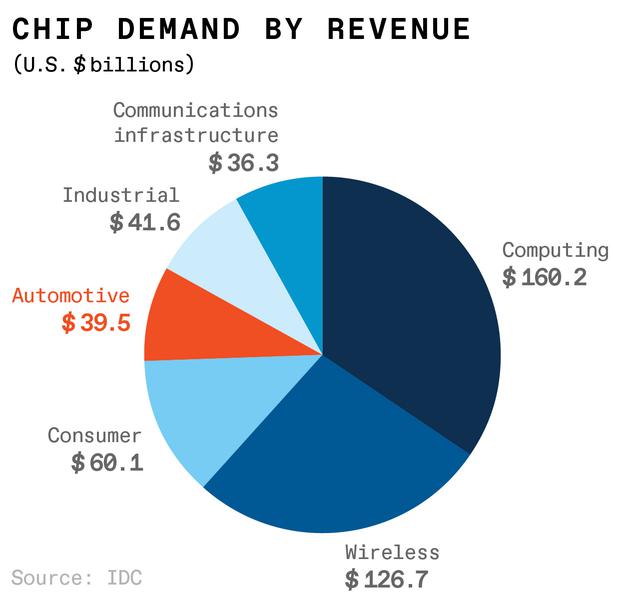

Devgan: It’s true more than ever.En los próximos cinco años más o menos se espera que el mercado de semiconductores se duplique a $ 1 billón.Eso es bueno para EDA y para IP.Además, las empresas de sistemas están diseñando más silicio, y eso no va a detener.Esa es una buena tendencia para nuestro negocio.Y finalmente, estamos invirtiendo fuertemente en el diseño y el análisis a nivel de sistema debido al acoplamiento del nivel del sistema y el nivel de chips, y ese es un TAM creciente.Por lo tanto, puede haber cierta corrección, pero eso sería más en el lado de la oferta que en el lado del diseño.Es muy difícil predecir que, por supuesto.Pero si miras estas mega tendencias, son muy positivas.

Faché: I agree.Hay nuevas aplicaciones y más verticales de la industria.Esas son buenas noticias.El corto plazo es un desafío, con la diferencia entre la demanda y la oferta..Estuve en un viaje reciente a Europa y hablé con algunos de nuestros clientes de semiconductores al respecto..A veces tienen demanda de sus productos que son 30% más altos de lo que pueden ofrecer.Los fabricantes están completamente reservados durante los próximos años, pero están agregando capacidad.Vi algo de esa construcción.Esperamos ver el equilibrio entre la oferta y la demanda en los próximos 18 a 24 meses.Más allá de eso, hay una tendencia de crecimiento secular en nuestro negocio.Hay más aplicaciones, más comienzos de diseño y nuevas nuevas empresas..Este es un mercado muy vibrante.Hay muchas inversiones en nuevos proyectos y nuevas nuevas empresas..Todos necesitan herramientas, y todos buscan IP que esté en contexto para el núcleo de su negocio..Y necesitan servicios de consultoría.Entonces estamos en un lugar realmente bueno.

Sawicki: Everyone remembers 10 years ago when everyone said Moore’s Law is dead, or when they said there was never going to be a 90nm node.Los inicios de diseño iban a colapsar a nada, y solo cuatro compañías iban a hacer chips.Nada de eso pasó.En todo caso, los inicios de diseño están aumentando radicalmente.Es un buen momento para estar en este negocio.Pero también es un desafío, porque estos son clientes exigentes.

SE: La ley de Moore no va a terminar pronto, pero se está desacelerando.Estamos viendo muchos más diseños heterogéneos en paquetes.¿Cuál es el impacto de eso?

Devgan: In 1997, I was telling people that system-in-a-package was going to take over system-on-a-chip.Tardó 25 años en que eso sucediera.System-in-a-paquete tiene muchas ventajas.Puede tener reutilización de silicio, no solo la reutilización de IP.La ley de Moore todavía puede continuar durante varias generaciones más, que son otros 5 a 10 años.Entonces, si la escala puede continuar durante 10 años, y puede agregar 3D-IC además de eso, puede seguir siendo exponencial durante otros 5 a 10 años.Si observa la escala durante los últimos 5 años, ha sido impulsado por tener más cosas en el chip, no la escalada clásica de Dennard.3D-IC es una extensión natural de eso, y estoy seguro de que el proceso base puede durar al menos cuatro o cinco generaciones más.

Fujimura: We do GPU acceleration for the semiconductor manufacturing industry, and we build our own GPU platforms because reliability concerns are so great.Así que rastreamos lo que está pasando con GPU bastante.Nvidia acaba de anunciar su nuevo procesador H100, que tiene 17,000 núcleos de precisión única.Estas son máquinas SIMD, por lo que realmente no puedes compararlas con las CPU.Pero en comparación con hace dos años cuando Nvidia anunció la generación anterior, la A100, que tenía alrededor de 7,000 núcleos de precisión única.En dos años, pasó de 7,000 núcleos a 17,000 núcleos.La ley de Moore es diferente ahora que en el pasado.Está escalando.No obtienes velocidades de reloj más rápidas, pero puedes calcular mucho más en un chip que hace dos años, y estoy seguro de que esto va a continuar.Intel acaba de anunciar su hoja de ruta de semiconductores, y van a los números y luego a Angstroms.Pero su hoja de ruta sale más de 10 años en el futuro.Entonces esto va a continuar.Por supuesto, es para cosas muy especializadas.Cuando estás haciendo dispositivos IoT, no necesitas eso.Pero principalmente debido al aprendizaje profundo, existe una enorme demanda de computación de alto rendimiento.Esa tendencia continuará, y los dólares de inversión continuarán estando disponibles.En el lado de la fabricación, las máscaras continuarán escala.La litografía para imprimir cosas en una oblea continuará.Pero será realmente caro.Entonces, la única pregunta es si hay una justificación económica para continuar, porque la demanda insaciable de informática que comenzó el aprendizaje profundo continuará.Esta es la computación de fuerza bruta, y será más que un solo aprendizaje profundo.No tienes que ser inteligente.Solo lo hagas.

Segars: If you look at some of the complex IoT devices that people are building right now, these are superscalar processors with very deep pipelines, and they’re quite amazing.En esta industria, las personas encontrarán formas de ofrecer más y más rendimiento en cada generación, y hay muchas herramientas para jugar con.3D-IC para estos paquetes muy complejos y multi-mores, agrega otra dimensión o dos a la rendimiento.Sin embargo, lo interesante es que no es solo más de lo mismo.No se trata de sacar más transistores en un chip o hacerlos más pequeños.Se trata de resolver diferentes problemas.En este momento, con la mayoría de las papas fritas, sale la oblea, se cortan, el dado va a algún lado, alguien más los empaqueta.Es bastante sencillo, y es un proceso muy bien optimizado.Pero tienes el espectro de tomar die de diferentes fábricas, armarlas usando una interfaz que va a resolver entre ellas y los estándares sobre cómo lidiar con el sustrato.Y luego debe reducir el costo, porque las personas que lo están haciendo hoy están construyendo diseños muy caros que solo unas pocas personas con recursos muy grandes pueden manejar.Pero esta es una tecnología que puede aplicarse en muchos lugares, y el desafío es cómo generar ese costo.Entonces, eso puede convertirse en algo que todo diseñador hace, al igual que escribir Verilog hoy, o encender un simulador o hacer un lugar y ruta.Eso tiene que volverse totalmente convencional.Y luego realmente encenderás el rendimiento, desde el microcontrolador más pequeño hasta el SoC o Chip más grande.

Faché: Cost is a big factor of that I am assuming will get addressed.Pero hay una buena pista para envases avanzados y 3D-IC.Tal vez comenzó con la memoria en la parte superior de las CPU para acortar distancias o reducir los retrasos en la transferencia de datos, pero hay muchas más aplicaciones fuera del dominio digital.Cuando piensa en apilar RF y circuitos analógicos, sensores y contenido digital, hay muchas aplicaciones.Así que hay un buen futuro para el embalaje avanzado y 3D-ICS.Por supuesto, está poniendo mucho énfasis en las herramientas para respaldar eso, y estos son diseños muy complejos..Cuando piensas en el Silicon IP, las interconexiones, el empaque y el modelado de todos los efectos, incluidos los efectos térmicos, parasitarios, las interconexiones, tendremos que poner las herramientas disponibles.

Sawicki: Dennard scaling is dead.La ley de Moore está bien.Pero hay una metáfora interesante aquí.Por lo tanto, todo el aspecto de Dennard Scaling Dying puso una prima por un largo período de tiempo en la cooperativa de tecnología de diseño: encontrar formas de optimizar cómo va a hacer un apilamiento de transistores, cuántas pistas, cómo van a poner estos dispositivosJuntos para que puedan tomar esta herramienta o este proceso que no le brinde inherentemente un mejor rendimiento, y aún así ofrecer un mejor rendimiento.A medida que va a 3D, debe tener una cooptimización de la cooptimización del sistema de diseño, y debemos comenzar a generar herramientas que permitan a las personas echar un vistazo a esto en la fase de planificación.¿Cómo vas a hacer tu partición?¿Cuáles son las implicaciones de rendimiento sobre tener la radio en un proceso versus cuánta memoria desea poner allí e injertar esas cosas?Vas a hacer un sustrato de silicio o un sustrato orgánico, porque eso tendrá un gran impacto en el costo.Esa es un conjunto de herramientas que están comenzando a surgir en este mercado.Se trata de poder apoyar esas decisiones a nivel de arquitectura, nuevamente, porque todo se remonta al rendimiento a nivel del sistema, que se puede entregar en el espacio de la aplicación que le importa a una compañía.

Devgan: 3D-IC is going to be pervasive, and it’s a great opportunity.Tenemos nuevos problemas para resolver, incluidos los efectos térmicos y los efectos electromagnéticos..Serán chips multitecnología, y la IP de interfaz entre chiplets.Esto es lo que queremos: se pagan problemas más grandes por ello..

Related

CEO Outlook: Chip Industry 2022 (Part 1 of above discussion)

Designing for context, and geopolitical impacts on a global supply chain.

Chip Industry Heads Toward $1T

Continued expansion in new and existing markets points to massive and sustained growth.

Slowdown, But No Correction

Materials supply chain still bumpy and consumer buying has peaked for now, but growth continues.

Big Changes In Materials And Processes For IC Manufacturing

Brewer Science’s CTO drills down into everything from purity and bonding to scaling and variation.