No pude evitar notar que en la presentación de CXL, Intel dio hoy una pista sobre el futuro de sus ambiciones de GPU XE. While it was not explicitly stated anywhere - it seems to have a pretty obvious implication to me; time to coin a term: Coherent Multi-GPU.CXL es la nueva capa de interconexión de Intel que está diseñada para resolver muchos problemas con el Protocolo PCIe y una de las principales razones por las cuales Multi -GPU nunca despegó correctamente se debe a la falta de, lo adivinó, coherencia.Creo que es muy probable que veamos las GPU de Xe ejecutándose en "modo CXL" en el futuro.

Intel CXL en pocas palabras: protocolo de cómputo heterogéneo para escalar procesadores sobre PCIe Gen 5 y más allá

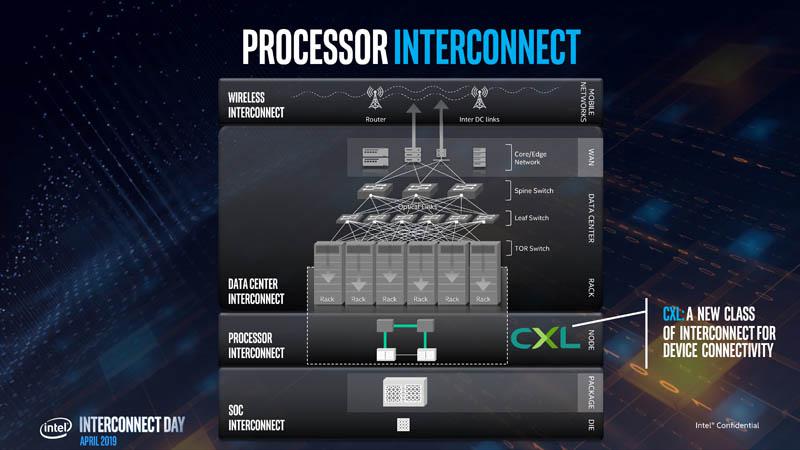

Intel discutió su nueva interconexión de procesador a procesador, llamado Compute Express Link (CXL), en detalle en el evento 'Interconnect Day 2019' ayer. Whereas we have talked in depth about data centre interconnects before, this particular one works to connect devices across the physical PCIe port. The reason why I mention physical and not just PCIe is because while Intel CXL is designed to work over the physical PCIe port to ensure universal compatibility - it will not utilize the PCIe protocol but instead act as an alternative protocol to the same; one that is far more future proof and scalable than its archaic (soon-to-be) predecessor.

Despliegue de actualizaciones de capacidad significativas sobre los puertos existentes es muy impresionante en el ecosistema actual y lo que Intel afirma no es solo una pequeña mejora de la capacidad: es masivo.El CXL de primera generación está diseñado para funcionar a través de PCIe Gen 5 (por lo que todavía está a unos años) y se espera que acelere el tiempo para PCIe 6.Hemos tenido PCIe 3 durante casi 8 años e Intel se está preparando para acortar el ciclo de actualización de la industria para este estándar.El interruptor entre los protocolos PCIe y CXL será completamente perfecto.

Cómo Intel CXL resuelve los problemas tradicionales de PCIe Multi-GPU

La presentación que Intel dio hoy en CXL se centró en el aspecto del centro de datos de todo, pero vemos un ángulo mucho más interesante para nuestra base de lectores, uno que la compañía no declaró explícitamente, pero es bastante obvio una vez que piensas en ello.. While CXL is pitched as the ultimate scaling fabric to glue together CPUs and accelerators there is no reason it cannot be used to achieve a finally-decent implementation of multi-GPU.Esto es en lo que me centraré en mi cobertura de CXL..Llamémoslo: Multi-GPU coherente.

Uno de los principales problemas con la escala PCIe en este momento es que cualquier dispositivo conectado a través de él tiene un grupo de memoria aislado, alta latencia en términos de comunicación de procesador a procesador y falta de coherencia en todo el sistema.Es por eso que compañías como Nvidia y AMD históricamente han tenido que innovar en el lado del software con todo tipo de técnicas de múltiples GPU, como la representación de cuadros divididos o la representación secuencial.Las GPU múltiples no actuaron como un todo coherente: actuaron de forma independiente y se demostró.CXL tiene como objetivo arreglar todo eso.

Con Intel CXL, se puede crear un grupo de memoria coherente y la latencia reducida por un orden de magnitud.Todo el sistema actuará como un todo cohesivo y escalará significativamente mejor.Esto significa que si tiene un sistema que ejecuta un Intel Xe DGPU, puede tirar otro en una ranura PCIe de repuesto y debería escalar sin problemas.Hay tres protocolos que presenta CXL:

CXL.IO, que es un protocolo IO, reemplaza a PCIe, por descubrimiento, configuración, acceso de registro, interrupciones, etc..Entonces tienes cxl.caché y cxl.memoria, cuales son los que estamos interesados principalmente.Estos protocolos permiten que los dispositivos conectados accedan a la memoria y al caché de manera coherente.En el papel, esto está diseñado para la CPU para acceder al acelerador VRAM y para que el acelerador acceda a la caché de la CPU, pero no veo ninguna razón por la cual estos protocolos no deberían permitir que múltiples GPU accedan a los búferes de memoria de los demás..

¿Conoces la molesta limitación de multi-GPU donde el VRAM nunca sumó?Bueno, CXL.memoria y CXL.el caché en conjunto debe resolver eso.Intel también ha declarado que, a diferencia de otras interconexiones, CXL está diseñado para una baja latencia, lo cual es perfecto para el enfoque de múltiples GPU.No está claro en este momento si también podemos implementar el tiempo a través de CXL o si eso aún requeriría conexiones de 'sincronización' como SLI Bridges.

El protocolo CXL de Intel también es asimétrico, lo que permite que el sistema no solo acepte aceleradores (léase: GPU), sino que también permite tampones de memoria coherentes, así como la inoperabilidad del protocolo..No solo eso, sino que este es un estándar mucho más abierto, que permite a los procesadores que no son Intel adoptan el protocolo, lo cual es clave si Intel quiere una amplia aceptación de este protocolo.El sesgo de coherencia en el protocolo CXL, a diferencia de los protocolos tradicionales, significa que la GPU en cuestión no tiene que detenerse en el procesador al acceder a la memoria, puede hacerlo por sí solo, aliviando la latencia del conductor.

Por supuesto, aparte de GPU por segundo, este enfoque se está lanzando principalmente para una configuración del centro de datos, por lo que las configuraciones de múltiples sockets y CCIX es lo que esto está al principio desde el primer momento..Debido a eso, también hay un flujo de sesgo del host, por lo que si realmente lo desea, aún puede usar el flujo más antiguo. Essentially, Intel is trying to create a heteregenous computing infrastructure that allows CPUs, GPUs, accelerators, FPGAs and pretty much anything that can go on a PCIe port to be glued togather as a cohesive whole.

El futuro: Intel Xe GPU en modo CXL?

Intel ha sido bastante fijo sobre los detalles de sus ambiciones de GPU XE.Todo lo que sabemos es que será escalable. It is a fairly good bet that multi-GPU is going to be involved in some way.¡Ya sea a través de CXL o a través de una implementación de MCM o incluso a ambos!No es una suposición de nadie si el modo CXL para GPU se dirigirá al segmento de consumo convencional para entusiastas como nosotros, pero está muy claro que resuelve muchos problemas que originalmente hicieron que las configuraciones de GPU multi -GPU no sean inútiles.

Ha pasado mucho tiempo desde que la innovación ha ocurrido en la pila de software y los protocolos que controlan el flujo de datos de la GPU a la CPU y sería genial ver este goteo hasta el nivel principal del consumidor.Si Intel comienza con una GPU XE singular, el modo CXL puede darle la ventaja para competir con variantes de gama alta de AMD y NVIDIA, y cambiar el nombre del juego por completo en el proceso.

Si CXL puede escalar sin problemas GPU, entonces la economía del mercado también cambiaría por completo.La gente podría comprar una GPU más barata primero y luego simplemente agregar otra si quieren más poder.Agregaría mucha más flexibilidad en las decisiones de compra e incluso aliviaría el remordimiento de los compradores hasta cierto punto para la clase de juego.Si el modo CXL se reduce al nivel del consumidor en el corto plazo, entonces podríamos incluso ver que los diseños de placa base cambian drásticamente a medida que múltiples enchufes y múltiples GPU se convierten en una opción factible.No hace falta decir que parece que las cosas se volverán bastante emocionantes en unos años..