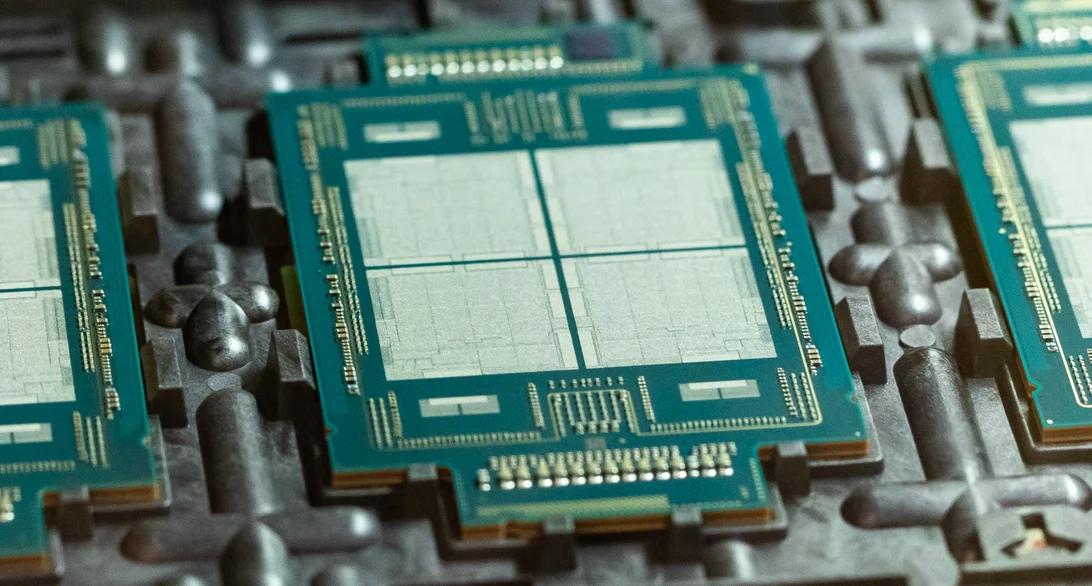

Un chip de prueba del lago Intel Meteor de Fab 42.(Créditos de imagen: CNET)

CNET has managed to capture the first die shots of several next-generation Intel Meteor Lake CPUs, Sapphire Rapids Xeons & Ponte Vecchio GPUs that are being tested & produced inside the chipmaker's Fab 42, situated in Arizona, US.

Glorious Die Shots of Intel's Next-Gen Meteor Lake CPUs, Sapphire Rapids Xeons & Ponte Vecchio GPUs Captured at Fab 42 in Arizona

Las tomas de matriz fueron capturadas por el reportero senior de CNET, Stephen Shankland, quien visitó Intel's Fab 42, ubicado en Arizona, EE. UU..Toda la magia ocurre aquí mientras la fábrica de fabricación está produciendo chips de próxima generación para consumidores, centros de datos y los segmentos informáticos de alto rendimiento.El FAB 42 manejará los chips de próxima generación de Intel producidos en los nodos de proceso de 10 nm (Intel 7) y 7Nm (Intel 4).Algunos de los productos clave que utilizarán estos nodos de próxima generación incluyen los procesadores de clientes de Meteor Lake, los procesadores Sapphire Rapids Xeon y las GPU de Ponte Vecchio para HPC.

Las CPU AMD Ryzen 7000 podrían tener una ventaja sobre las capacidades de memoria Raptor Lake DDR5 de Intel como velocidades "nativas" de 5200 Mbps enumeradas para 13ª generación

Intel 4 Powered Meteor Lake CPUs For Client Computing

El primer producto del que hablar es Meteor Lake.Dirigiéndose a las PC de escritorio de clientes en 2023, las CPU de Meteor Lake serán el primer diseño verdadero de Multi-Chiplet de Intel.CNET logró obtener tomas de los primeros chips de prueba del lago Meteor que se ven notablemente similares a los renders que Intel se burló en su evento del Día de la Arquitectura 2021.El vehículo de prueba del lago Meteor que se muestra arriba se utiliza para garantizar que el diseño de envasado de forveros funcione correctamente y, como se esperaba..Meteor Lake CPU utilizará la tecnología de envasado forveros de Intel para interconectar las diversas IP de núcleo integradas en el chip.

Intel Meteor Lake Test Chips Prepare Chipzilla para la producción final de CPU de núcleo de próxima generación.(Créditos de imagen: CNET)

El dado tiene cuatro chiplets que están conectados juntos en el mismo sustrato.Según lo que Intel ha mostrado en sus renders, el troquel superior debe ser el mosaico de cómputo, el mosaico medio debe ser el mosaico SoC-LP y la muerte más baja debe ser el mosaico GPU.Sin embargo, según los tamaños de matriz, eso no va bien.El dado medio podría ser el mosaico de cómputo principal que alberga los núcleos y el troquel más pequeño debajo podría ser el mosaico SoC-LP que incluye el IO.El troquel más alto debe ser la GPU, mientras que el dado más pequeño al lado podría ser un caché separado u otro mosaico IO.Esto es solo una especulación pura por ahora, ya que estos son chips de prueba y el diseño final puede terminar siendo diferente.

También tenemos un primer vistazo a la oblea de chip de prueba del lago Meteor que mide 300 mm en diagonal.La oblea comprende chips de prueba que son troqueles ficticios, una vez más para asegurarse de que las interconexiones en el chip funcionen según lo previsto.Intel ya logró encendido para su mosaico de CPU Meteor Lake Compute, por lo que podemos esperar que los chips finales sean producidos por el segundo de 2022 para el lanzamiento en 2023.

Intel adds Arc GPU, Rocky Linux, & multi-GPU functionality support to oneVPL 2022.1

Here's Everything We Know About The 14th Gen Meteor Lake 7nm CPUs

Ya obtuvimos algunos detalles de Intel, como el hecho de que se espera que las CPU de escritorio y movilidad de Intel Lake se basen en una nueva línea de arquitectura de núcleo de Cove.Se rumorea que esto se conoce como 'Redwood Cove' y se basará en un nodo de proceso EUV de 7 nm.Se afirma que la ensenada de Redwood está diseñada desde cero para ser un nodo agnóstico, lo que significa que se puede fabricar en diferentes fabs.Hay referencias mencionadas que señalan que TSMC es una copia de seguridad o incluso un proveedor parcial para los chips basados en Redwood Cove.Esto podría decirnos por qué Intel está declarando múltiples procesos de fabricación para la familia de la CPU.

Las CPU de Meteor Lake posiblemente sean la primera generación de CPU de Intel para despedirse de la arquitectura de interconexión del autobús anillo.También hay rumores de que Meteor Lake podría ser un diseño totalmente apilado en 3D y podría utilizar un dado de E/S de un fabuloso externo (TSMC avistado nuevamente).Se destaca que Intel utilizará oficialmente su tecnología de envasado Foveros en la CPU para interconectar los diversos troqueles en el chip (XPU).Esto también se alinea con Intel que se refiere a cada mosaico en chips de 14a generación individualmente (calcular el mosaico = núcleos de CPU).

The Meteor Lake Desktop CPU family is expected to retain support on the LGA 1700 socket which is the same socket used by Alder Lake & Raptor Lake processors.Podemos esperar la memoria DDR5 y PCIe Gen 5.0 soporte. The platform will support both DDR5 & DDR4 memory with the mainstream and budget tier options going for DDR4 memory DIMMs while the premium & high-end offerings going for DDR5 DIMMs.El sitio también enumera tanto Meteor Lake P como Meteor Lake M CPU que estará dirigido a plataformas de movilidad.

Intel Beinstream Desktop CPU Generations Comparación:

| Intel CPU Family | Processor Process | Processors Cores/Threads (Max) | TDPs | Platform Chipset | Platform | Memory Support | PCIe Support | Launch |

|---|---|---|---|---|---|---|---|---|

| Sandy Bridge (2nd Gen) | 32nm | 4/8 | 35-95W | 6-Series | LGA 1155 | DDR3 | PCIe Gen 2.0 | 2011 |

| Ivy Bridge (3rd Gen) | 22nm | 4/8 | 35-77W | 7-Series | LGA 1155 | DDR3 | PCIe Gen 3.0 | 2012 |

| Haswell (4th Gen) | 22nm | 4/8 | 35-84W | 8-Series | LGA 1150 | DDR3 | PCIe Gen 3.0 | 2013-2014 |

| Broadwell (5th Gen) | 14nm | 4/8 | 65-65W | 9-Series | LGA 1150 | DDR3 | PCIe Gen 3.0 | 2015 |

| Skylake (6th Gen) | 14nm | 4/8 | 35-91W | 100-Series | LGA 1151 | DDR4 | PCIe Gen 3.0 | 2015 |

| Kaby Lake (7th Gen) | 14nm | 4/8 | 35-91W | 200-Series | LGA 1151 | DDR4 | PCIe Gen 3.0 | 2017 |

| Coffee Lake (8th Gen) | 14nm | 6/12 | 35-95W | 300-Series | LGA 1151 | DDR4 | PCIe Gen 3.0 | 2017 |

| Coffee Lake (9th Gen) | 14nm | 8/16 | 35-95W | 300-Series | LGA 1151 | DDR4 | PCIe Gen 3.0 | 2018 |

| Comet Lake (10th Gen) | 14nm | 10/20 | 35-125W | 400-Series | LGA 1200 | DDR4 | PCIe Gen 3.0 | 2020 |

| Rocket Lake (11th Gen) | 14nm | 8/16 | 35-125W | 500-Series | LGA 1200 | DDR4 | PCIe Gen 4.0 | 2021 |

| Alder Lake (12th Gen) | Intel 7 | 16/24 | 35-125W | 600 Series | LGA 1700 | DDR5 / DDR4 | PCIe Gen 5.0 | 2021 |

| Raptor Lake (13th Gen) | Intel 7 | 24/32 | 35-125W | 700-Series | LGA 1700 | DDR5 / DDR4 | PCIe Gen 5.0 | 2022 |

| Meteor Lake (14th Gen) | Intel 4 | TBA | 35-125W | 800 Series? | TBA | DDR5 | PCIe Gen 5.0? | 2023 |

| Arrow Lake (15th Gen) | Intel 20A | 40/48 | TBA | 900-Series? | TBA | DDR5 | PCIe Gen 5.0? | 2024 |

| Lunar Lake (16th Gen) | Intel 18A | TBA | TBA | 1000-Series? | TBA | DDR5 | PCIe Gen 5.0? | 2025 |

| Nova Lake (17th Gen) | Intel 18A | TBA | TBA | 2000-Series? | TBA | DDR5? | PCIe Gen 6.0? | 2026 |

Intel 7 Powered Sapphire Rapids CPUs For Xeon Data Center & Servers

También obtenemos una visión más detallada del sustrato de CPU de Intel Sapphire Rapids-Sp Xeon, las chiplets y el diseño completo de paquetes (variantes estándar y HBM).La variante estándar presenta cuatro mosaicos que incorporarán los chiplets de cómputo.También hay cuatro pinzas para los paquetes HBM.El chip se comunicará con los 8 chiplets (cuatro cómputo / cuatro hbm) a través de interconexiones emib que son las barras rectangulares más pequeñas en el borde de cada dado..

A substrate of the Intel Sapphire Rapids-SP Xeon CPU with HBM2e memory.(Créditos de imagen: CNET)El producto final se puede ver a continuación y muestra las cuatro fichas de cómputo de Xeon en el medio con cuatro paquetes HBM2 más pequeños en los lados.Intel confirmó recientemente que sus CPU de Sapphire Rapids-Sp Xeon contarán con hasta 64 GB de memoria HBM2E a bordo de las CPU.Este es el diseño de CPU completo que se muestra aquí y muestra que está listo para la implementación en los centros de datos de próxima generación para 2022.

The final 4th Gen Sapphire Rapids-SP Xeon CPU with its multi-chiplet design housing Compute & HBM2e tiles.(Créditos de imagen: CNET)Here's Everything We Know About The 4th Gen Intel Sapphire Rapids-SP Xeon Family

Según Intel, el Sapphire Rapids-SP vendrá en dos variantes de paquetes, un estándar y una configuración de HBM.La variante estándar contará con un diseño de chiplet compuesto por cuatro troqueles XCC que contará con un tamaño de dado de alrededor de 400 mm2.Este es el tamaño de la matriz para un dado de XCC singular y habrá cuatro en total en el chip de zafiro superior Rapids-sp Xeon.Cada dado se interconectará a través de EMIB, que tiene un tamaño de lanzamiento de 55U y un tono central de 100U.

El chip de Sapphire Rapids-SP Xeon contará con 10 interconexiones EMIB y todo el paquete se medirá en un poderoso 4446 mm2.Avanzando a la variante HBM, estamos obteniendo un mayor número de interconexiones que se encuentran en 14 y son necesarias para interconectar la memoria HBM2E a los núcleos.

Los cuatro paquetes de memoria HBM2E contarán con 8-HI pilas para que Intel pase al menos 16 GB de memoria HBM2E por pila para un total de 64 GB en el paquete Sapphire Rapids-SP.Hablando sobre el paquete, la variante HBM medirá en un loco 5700 mm2 o 28% más grande que la variante estándar.En comparación con los números de genoa de EPYC recientemente filtrados, el paquete HBM2E para Sapphire Rapids-SP terminaría un 5% más grande, mientras que el paquete estándar será un 22% más pequeño.

Intel también afirma que el enlace EMIB proporciona el doble de mejora de la densidad de ancho de banda y 4 veces mejor eficiencia energética en comparación con los diseños de paquetes estándar.Curiosamente, Intel llama a la última alineación de Xeon lógicamente monolítica, lo que significa que se refieren a la interconexión que ofrecerá la misma funcionalidad que una sola morada, pero técnicamente, hay cuatro chiplets que se interconectarán juntos.. You can read the full details regarding the standard 56 core & 112 thread Sapphire Rapids-SP Xeon CPUs here.

Familias Intel Xeon SP (preliminar):

| Family Branding | Skylake-SP | Cascade Lake-SP/AP | Cooper Lake-SP | Ice Lake-SP | Sapphire Rapids | Emerald Rapids | Granite Rapids | Diamond Rapids |

|---|---|---|---|---|---|---|---|---|

| Process Node | 14nm+ | 14nm++ | 14nm++ | 10nm+ | Intel 7 | Intel 7 | Intel 3 | Intel 3? |

| Platform Name | Intel Purley | Intel Purley | Intel Cedar Island | Intel Whitley | Intel Eagle Stream | Intel Eagle Stream | Intel Mountain Stream Intel Birch Stream | Intel Mountain Stream Intel Birch Stream |

| Core Architecture | Skylake | Cascade Lake | Cascade Lake | Sunny Cove | Golden Cove | Raptor Cove | Redwood Cove? | Lion Cove? |

| IPC Improvement (Vs Prev Gen) | 10% | 0% | 0% | 20% | 19% | 8%? | 35%? | 39%? |

| MCP (Multi-Chip Package) SKUs | No | Yes | No | No | Yes | Yes | TBD (Possibly Yes) | TBD (Possibly Yes) |

| Socket | LGA 3647 | LGA 3647 | LGA 4189 | LGA 4189 | LGA 4677 | LGA 4677 | TBD | TBD |

| Max Core Count | Up To 28 | Up To 28 | Up To 28 | Up To 40 | Up To 56 | Up To 64? | Up To 120? | Up To 144? |

| Max Thread Count | Up To 56 | Up To 56 | Up To 56 | Up To 80 | Up To 112 | Up To 128? | Up To 240? | Up To 288? |

| Max L3 Cache | 38.5 MB L3 | 38.5 MB L3 | 38.5 MB L3 | 60 MB L3 | 105 MB L3 | 120 MB L3? | 240 MB L3? | 288 MB L3? |

| Vector Engines | AVX-512/FMA2 | AVX-512/FMA2 | AVX-512/FMA2 | AVX-512/FMA2 | AVX-512/FMA2 | AVX-512/FMA2 | AVX-1024/FMA3? | AVX-1024/FMA3? |

| Memory Support | DDR4-2666 6-Channel | DDR4-2933 6-Channel | Up To 6-Channel DDR4-3200 | Up To 8-Channel DDR4-3200 | Up To 8-Channel DDR5-4800 | Up To 8-Channel DDR5-5600? | Up To 12-Channel DDR5-6400? | Up To 12-Channel DDR6-7200? |

| PCIe Gen Support | PCIe 3.0 (48 Lanes) | PCIe 3.0 (48 Lanes) | PCIe 3.0 (48 Lanes) | PCIe 4.0 (64 Lanes) | PCIe 5.0 (80 lanes) | PCIe 5.0 (80 Lanes) | PCIe 6.0 (128 Lanes)? | PCIe 6.0 (128 Lanes)? |

| TDP Range (PL1) | 140W-205W | 165W-205W | 150W-250W | 105-270W | Up To 350W | Up To 375W? | Up To 400W? | Up To 425W? |

| 3D Xpoint Optane DIMM | N/A | Apache Pass | Barlow Pass | Barlow Pass | Crow Pass | Crow Pass? | Donahue Pass? | Donahue Pass? |

| Competition | AMD EPYC Naples 14nm | AMD EPYC Rome 7nm | AMD EPYC Rome 7nm | AMD EPYC Milan 7nm+ | AMD EPYC Genoa ~5nm | AMD Next-Gen EPYC (Post Genoa) | AMD Next-Gen EPYC (Post Genoa) | AMD Next-Gen EPYC (Post Genoa) |

| Launch | 2017 | 2018 | 2020 | 2021 | 2022 | 2023? | 2024? | 2025? |

Intel 7 Powered Ponte Vecchio GPUs For HPC

Por último, tenemos una gran vista de la GPU Intel Ponte Vecchio, la solución HPC de próxima generación.Ponte Vecchio fue diseñado y creado bajo el liderazgo de Raja Koduri, quien nos ha estado proporcionando grandes cositas sobre la filosofía de diseño y el poder de cómputo que hace que este chip se ponga..

Intel's Ponte Vecchio is a gold mine of chiplets, housing over 47 different tiles on the same package.(Créditos de imagen: CNET)Here's Everything We Know About The Intel 7 Powered Ponte Vecchio GPUs

Al pasar a Ponte Vecchio, Intel describió algunas características clave de su GPU de centro de datos insignia, como 128 Xe núcleos, 128 unidades RT, memoria HBM2E y un total de 8 GPU XE-HPC que se conectarán junto.El chip contará con hasta 408 MB de caché L2 en dos pilas separadas que se conectarán a través de la interconexión EMIB.El chip contará con múltiples troqueles basados en el propio proceso 'Intel 7' de Intel y los nodos de proceso N7 / N5 de TSMC.

Intel también detalló previamente el paquete y el tamaño de la muerte de su GPU de Ponte Vecchio insignia basada en la arquitectura XE-HPC.El chip consistirá en 2 mosaicos con 16 troqueles activos por pila.El tamaño máximo de died superior activo activo será de 41 mm2, mientras que el tamaño de la matriz base, que también se conoce como el 'mosaico de cómputo' se encuentra a 650 mm2.Tenemos todos los chiplets y nodos de proceso que utilizará las GPU de Ponte Vecchio, enumeradas a continuación:

El siguiente es cómo Intel llega a 47 mosaicos en el chip Ponte Vecchio:

La GPU de Ponte Vecchio utiliza 8 pilas de 8 HBM 8-HI y contiene un total de 11 interconexiones EMIB.Todo el paquete Intel Ponte Vecchio mediría 4843.75 mm2.También se menciona que el tono de golpe para las CPU del lago Meteor que utilizan el empaque de forveros 3D de alta densidad será 36U.

The Ponte Vecchio GPU will be competing against NVIDIA and AMD HPC GPUs in 2022.(Créditos de imagen: CNET)La GPU de Ponte Vecchio no es 1 chip sino una combinación de varias chips.Es una potencia de chiplet, que empaca la mayoría de los chiplets en cualquier GPU/CPU, 47 para ser precisos.Y estos no se basan en un solo nodo de proceso, sino varios nodos de proceso, ya que habíamos detallado solo unos días.

Aceleradores de GPU del centro de datos de próxima generación

| GPU Name | AMD Instinct MI250X | NVIDIA Hopper GH100 | Intel Ponte Vecchio |

|---|---|---|---|

| Packaging Design | MCM (Infinity Fabric) | Monolithic | MCM (EMIB + Foveros) |

| GPU Architecture | Aldebaran (CDNA 2) | Hopper GH100 | Xe-HPC |

| GPU Process Node | 6nm | 4N | 7nm (Intel 4) |

| GPU Cores | 14,080 | 16,896 | 16,384 ALUs (128 Xe Cores) |

| GPU Clock Speed | 1700 MHz | ~1780 MHz | TBA |

| L2 / L3 Cache | 2 x 8 MB | 50 MB | 2 x 204 MB |

| FP16 Compute | 383 TOPs | 2000 TFLOPs | TBA |

| FP32 Compute | 95.7 TFLOPs | 1000 TFLOPs | ~45 TFLOPs (A0 Silicon) |

| FP64 Compute | 47.9 TFLOPs | 60 TFLOPs | TBA |

| Memory Capacity | 128 GB HBM2E | 80 GB HBM3 | 128 GB HBM2e |

| Memory Clock | 3.2 Gbps | 3.2 Gbps | TBA |

| Memory Bus | 8192-bit | 5120-bit | 8192-bit |

| Memory Bandwidth | 3.2 TB/s | 3.0 TB/s | ~3 TB/s |

| Form Factor | OAM | OAM | OAM |

| Cooling | Passive Cooling Liquid Cooling | Passive Cooling Liquid Cooling | Passive Cooling Liquid Cooling |

| TDP | 560W | 700W | TBD |

| Launch | Q4 2021 | 2H 2022 | 2022? |

Se espera que el Fab 42 de Intel se fusione con los próximos Fab 52 y Fab 62 en los próximos años que producirán lo que viene a continuación..El CEO de Intel, Pat Gelsinger, ya comenzó en los Fabs en septiembre y aquí es donde verá la producción de los productos Sub-Intel 7 de próxima generación.

Hoja de ruta de proceso Intel

| Process Name | Intel 10nm SuperFin | Intel 7 | Intel 4 | Intel 3 | Intel 20A | Intel 18A |

|---|---|---|---|---|---|---|

| Production | In High-Volume (Now) | In Volume (Now) | 2H 2022 | 2H 2023 | 2H 2024 | 2H 2025 |

| Perf/Watt (over 10nm ESF) | N/A | 10-15% | 20% | 18% | >20%? | TBA |

| EUV | N/A | N/A | Yes | Yes | Yes | High-NA EUV |

| Transistor Architecture | FinFET | Optimized FinFET | Optimized FinFET | Optimized FinFET | RibbonFET | Optimized RibbonFET |

| Products | Tiger Lake | Alder Lake Raptor Lake Sapphire Rapids Emerald Rapids Xe-HPG? | Meteor Lake Xe-HPC / Xe-HP? | Granite Rapids Sierra Forest TBA | Arrow Lake Diamond Rapids? TBA | Lunar Lake Nova Lake TBA TBA |

Fuente de noticias: CNET