El diseño digital de nuestras computadoras cotidianas es bueno para leer correos electrónicos y jugar, pero las computadoras de resolución de problemas actuales trabajan con grandes cantidades de datos. La capacidad de almacenar y procesar esta información puede generar cuellos de botella en el rendimiento debido a la forma en que se construyen las computadoras.

La próxima revolución informática podría ser un nuevo tipo de hardware, llamado procesamiento en memoria (PIM), un paradigma informático emergente que fusiona la memoria y la unidad de procesamiento y realiza sus cálculos utilizando las propiedades físicas de la máquina, no 1s o 0s necesarios para hacer el procesamiento digitalmente.

En la Universidad de Washington en St. Louis, investigadores del laboratorio de Xuan "Silvia" Zhang, profesora asociada en el Departamento de Electricidad & de Preston M. Green. Ingeniería de Sistemas de la Escuela de Ingeniería McKelvey, ha diseñado un nuevo circuito PIM, que aporta la flexibilidad de las redes neuronales para influir en la computación PIM. El circuito tiene el potencial de aumentar el rendimiento de la computación PIM en órdenes de magnitud más allá de sus capacidades teóricas actuales.

Su investigación se publicó en línea el 27 de octubre en la revista IEEE Transactions on Computers. El trabajo fue una colaboración con Li Jiang en la Universidad Shanghai Jiao Tong en China.

Las computadoras de diseño tradicional se construyen utilizando una arquitectura Von Neuman. Parte de este diseño separa la memoria, donde se almacenan los datos, y el procesador, donde se realiza la computación real.

anuncio"Los desafíos informáticos de hoy requieren una gran cantidad de datos", dijo Zhang. "Necesitamos procesar toneladas de datos, lo que crea un cuello de botella en el rendimiento en la interfaz del procesador y la memoria".

Las computadoras PIM tienen como objetivo eludir este problema fusionando la memoria y el procesamiento en una sola unidad.

La informática, especialmente la informática para los algoritmos de aprendizaje automático actuales, es esencialmente una serie compleja, extremadamente compleja, de sumas y multiplicaciones. En una unidad central de procesamiento (CPU) digital tradicional, esto se hace usando transistores, que básicamente son puertas controladas por voltaje para permitir que la corriente fluya o no fluya. Estos dos estados representan 1 y 0, respectivamente. Usando este código digital, código binario, una CPU puede hacer todas y cada una de las operaciones aritméticas necesarias para que una computadora funcione.

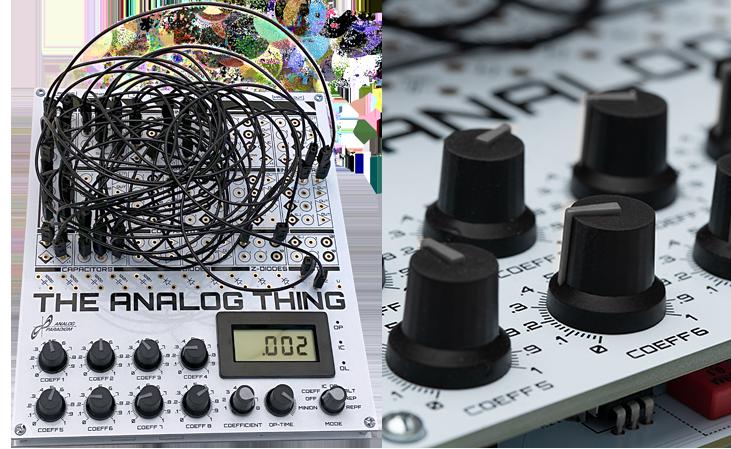

El tipo de PIM en el que trabaja el laboratorio de Zhang se llama PIM de memoria resistiva de acceso aleatorio, o RRAM-PIM. Mientras que en una CPU, los bits se almacenan en un condensador en una celda de memoria, las computadoras RRAM-PIM se basan en resistencias, de ahí el nombre. Estas resistencias son tanto la memoria como el procesador.

¿La bonificación? "En la memoria resistiva, no tiene que traducir a digital o binario. Puede permanecer en el dominio analógico". Esta es la clave para hacer que las computadoras RRAM-PIM sean mucho más eficientes.

publicidad"Si necesita agregar, conecte dos corrientes", dijo Zhang. "Si necesita multiplicar, puede modificar el valor de la resistencia".

Pero en algún momento, la información debe traducirse a un formato digital para interactuar con las tecnologías con las que estamos familiarizados. Ahí es donde RRAM-PIM encontró su cuello de botella: convertir la información analógica en un formato digital. Luego, Zhang y Weidong Cao, un investigador asociado postdoctoral en el laboratorio de Zhang, introdujeron aproximadores neuronales.

"Un aproximador neuronal se basa en una red neuronal que puede aproximar funciones arbitrarias", dijo Zhang. Dada cualquier función, el aproximador neural puede realizar la misma función, pero mejorar su eficiencia.

En este caso, el equipo diseñó circuitos aproximadores neuronales que podrían ayudar a eliminar el cuello de botella.

En la arquitectura RRAM-PIM, una vez que las resistencias en una matriz de barras transversales han realizado sus cálculos, las respuestas se traducen a un formato digital. Lo que eso significa en la práctica es sumar los resultados de cada columna de resistencias en un circuito. Cada columna produce un resultado parcial.

Cada uno de esos resultados parciales, a su vez, debe convertirse en información digital en lo que se denomina conversión de analógico a digital o ADC. La conversión consume mucha energía.

El aproximador neuronal hace que el proceso sea más eficiente.

En lugar de sumar cada columna una por una, el circuito de aproximación neuronal puede realizar múltiples cálculos: columnas hacia abajo, entre columnas o de la manera que sea más eficiente. Esto conduce a menos ADC y una mayor eficiencia informática.

La parte más importante de este trabajo, dijo Cao, fue determinar hasta qué punto podían reducir la cantidad de conversiones digitales que se producían a lo largo del borde exterior del circuito. Descubrieron que los circuitos de aproximación neuronal aumentaron la eficiencia en la medida de lo posible.

"No importa cuántas sumas parciales analógicas generen las columnas de la matriz de barras cruzadas de la RRAM (18, 64 o 128), solo necesitamos una conversión de analógico a digital", dijo Cao. "Utilizamos la implementación de hardware para lograr el límite bajo teórico".

Los ingenieros ya están trabajando en prototipos a gran escala de computadoras PIM, pero se han enfrentado a varios desafíos, dijo Zhang. El uso de los aproximadores neuronales de Zhang y Cao podría eliminar uno de esos desafíos: el cuello de botella, lo que demuestra que este nuevo paradigma informático tiene el potencial de ser mucho más poderoso de lo que sugiere el marco actual. No solo una o dos veces más potente, sino 10 o 100 veces más.

"Nuestra tecnología nos permite acercarnos un paso más a este tipo de computadora", dijo Zhang.